Cortex-A8

ARM超標量處理器型號

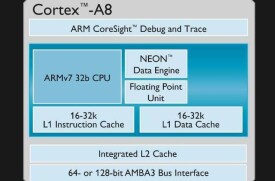

ARM Cortex-A8處理器是第1款基於ARMv7架構的應用處理器,是有史以來ARM開發的性能最高、功率效率最高的處理器。Cortex-A8處理器的速率在600MHz到超過1GHz的範圍內,能夠滿足那些需要工作在300mW以下的功耗優化的移動設備的要求;以及滿足那些需要2000 Dhrystone MIPS的性能優化的消費類應用的要求。

Cortex-A8工業開發板-安賽卓爾電子科技

Cortex-A8處理器出色的運行速率和功率效率是通過新的支持並實現了高級泄露控制的ARM Artisan® Advantage-CE庫實現的。這種處理器得到了各種各樣的適用於快速系統設計的ARM技術的支持,其中包括:

RealView® DEVELOP系列軟體開發工具

RealView CREATE系列ESL工具和模型

CoreSight™調試和跟蹤技術;以及通過OpenMAX多媒體處理標準實現的軟體庫支持。

AMBA® 3 AXI高性能SoC互連

ARM Cortex-A8處理器複雜的流水線架構基於雙對稱的,順序發射的,13級流水線,帶有先進的動態分支預測,可實現2.0 DMIPS/MHz。

順序,雙發射,超標量微處理器內核,13級主整數流水線

10級NEON媒體流水線 10-stage NEON media pipeline

專用的L2緩存,帶有可編程的等待狀態

基於全局歷史的分支預測

結合功率優化的載入存儲流水線,為功率敏感型應用提供2.0 DMIPS/MHz的速率 遵從ARMv7架構規範,其中包括:

用於實現更高的性能、能量效率和代碼密度的Thumb-2技術

NEON™信號處理擴展,用於加速H.264和MP3等媒體編解碼器

Jazelle RCT Java-加速技術,用於最優化即時(JIT)編譯和動態自適應編譯(DAC),並將存儲器尺寸減小了多達3倍

TrustZone技術,用於安全交易和數字許可權管理(DRM)

集成的L2緩存

使用標準編譯的ARM建立而成

64K到2MB的可配置容量

可編程的延遲

優化的L1緩存

經過性能和功耗的優化

結合最小訪問延遲和散列確定方式,以便將性能最大化,將功耗最小化。

動態分支預測

通過分支目標和全局歷史緩衝區實現

按照行業基準,達到95%的準確率。

重放機制,以實現預測失敗代價的最小化

存儲器系統

訪問L1緩存導致的單周期載入使用代價

L1緩存的散列數組使得只有在可能需要時才會啟用存儲器。

集成的、可配置L2緩存和用於數據流的NEON媒體單元之間的直連介面

Bank化的L2緩存設計,每次只設計1個Bank

支持多項與L3存儲器之間的未完成事務,以充分利用CPU。

ARM公司日前發布最新的Cortex-A8處理器,它將給消費和低功耗移動產品帶來重大變革,使得最終用戶可以享受到更高水準的娛樂和創新。在於美國加州舉行的第二屆ARM開發者年度大會上發布的ARM Cortex-A8處理器最高能達到2000DMIPS,使它成為運行多通道視頻、音頻和遊戲應用的要求越來越高的消費產品的最佳選擇。在65納米工藝下,ARM Cortex-A8處理器的功耗不到300毫瓦,能夠提供業界領先的性能和功耗效率。ARM Cortex-A8處理器第一次為低費用、高容量的產品帶來了台式機級別的性能。支持智能能源管理(Intelligent Energy Manger,IEM)技術的ARM Artisan庫以及先進的泄漏控制技術使得Cortex-A8處理器實現了非凡的速度和功耗效率。Cortex-A8處理器得到了大量ARM技術的支持,從而能夠實現快速的系統設計。這些支持包括:RealView DEVELOPOER軟體開發工具,RealView ARCHITECT ESL工具和模型,CoreSight調試和追蹤技術,以及對OpenMAX多媒體處理標準的軟體庫支持。在同一天,德州儀器和ARM在第二屆ARM開發者年度大會上共同宣布德州儀器第一個獲得全新的ARM Cortex-A8處理器的授權。德州儀器同時也是在這一新處理器開發過程中領先的ARM合作夥伴。德州儀器將把Cortex-A8處理器用於其眾多下一代超低功耗3G數據機以及高性能的OMPATM應用處理器。後者將以65納米工藝進行生產,同時德州儀器的SmartReflex功耗和性能管理技術和M-ShieldTM安全解決方案也將提高其性能。除了德州儀器之外,ARM已經成功地與另外四家公司達成了Cortex-A8處理器的授權協議,其中包括飛思卡爾、Matsushita和三星。同時,Cortex-A8處理器還獲得了主要EDA和操作系統提供商今後的支持。 Cortex-A8處理器是第一款基於下一代ARMv7架構的應用處理器,使用了能夠帶來更高性能、功耗效率和代碼密度的Thumb-2技術。它首次採用了強大的NEONTM信號處理擴展集,對H.264和MP3等媒體編解碼提供加速。Cortex-A8解決方案還包括Jazelle-RCT Java加速技術,對實時(JIT)和動態調適編譯(DAC)提供最優化,同時減少內存佔用空間高達三倍。此外,新處理器還配置了用於安全交易和數字版權管理的TrustZone技術以及實現低功耗管理的IEM功能。 ARM市場營銷執行副總裁Mike Inglis表示:“數字娛樂和移動通信技術的迅速融合對系統性能和安全提出了全新的要求,並且需要以有限的費用和功耗實現。全新的ARM Cortex-A8處理器及其背後提供支持的技術為家庭和移動市場帶來了前所未有的性能和功耗水平,同時也將為消費者帶來具有豐富媒體應用的創新的新設備。” Cortex-A8處理器配置了先進的超標量體系結構管線,能夠同時執行多條指令,並且提供超過2.0 DMIPS/MHz。處理器集成了一個可調尺寸的二級高速緩衝存儲器,能夠同高速的16K或者32K一級高速緩衝存儲器一起工作,從而達到最快的讀取速度和最大的吞吐量。Cortex-A8處理器使用了先進的分支預測技術,並且具有專用的NEON整型和浮點型管線進行媒體和信號處理。在使用小於4平方毫米的矽片及低功耗的65納米工藝的情況下,Cortex-A8處理器的運行速度將高於600MHz(不包括NEON,追蹤技術和二級高速緩衝存儲器)。在高性能的90納米和65納米工藝下,Cortex-A8處理器運行速度最高可達到1GHz,從而滿足高性能消費產品設計的需要。

| Cortex-A8 | |

| 架構 | ARMv7-A Cortex |

| Dhrystone 性能 | 2.0 DMIPS / MHz |

| 多核 | 否 – 僅單核 |

| ISA 支持 | ARM Thumb-2/ Thumb NEON VFPv3 浮點 |

| 內存管理 | 內存管理單元 (MMU) |

| 調試和跟蹤 | CoreSight DK-A8(單獨提供) |

| Cortex-A8 功能 | 功能說明 |

| NEON | 128 位 SIMD 引擎支持高性能媒體處理。將 NEON 用於某些音頻、視頻和圖形工作負載可以減輕跨 SoC 支持多個專用加速器的負擔,並且使系統可以支持將來的標準 |

| 優化的 1 級高速緩存 | 1 級高速緩存在單循環訪問時間緊密集成到處理器中。該高速緩存將最低訪問延遲與哈希方式確定性結合在一起,可以在最大程度上提高性能和降低功耗。 |

| 集成的 2 級高速緩存 | 2 級高速緩存集成到內核中,以實現輕鬆集成、高功效和最佳性能。該高速緩存使用標準編譯的 RAM 構建,可配置範圍從 0K 到 1MB。該高速緩存可以使用編譯的內存構建,具有可編程延遲,以適應不同的數組特徵 |

| Thumb-2 技術 | 可為傳統 ARM 代碼提供最高性能,對於存儲指令佔用的內存,最多可節省 30% 的空間。 |

| 動態分支預測 | 為了最大程度地降低分支錯誤預測的危害,動態分支預測器跨各種行業基準實現 95% 的準確性。可以通過分支目標和全局歷史記錄緩衝區啟用預測器。重放機制將漏測危害降到最低。 |

| 內存管理單元 | 完整的 MMU 使 Cortex-A8 可以在各種應用程序中運行富操作系統 |

| Jazelle-RCT 技術 | RCT Java 加速技術可以優化即時生產 (JIT) 和動態自適應編譯 (DAC),以及將內存佔用空間減少高達三倍 |

| 內存系統 | 針對高功效和高性能進行了優化。L1 高速緩存中的散列數組限定僅當可能需要內存時才激活它們。集成的、可配置 L2 高速緩存與用於數據流式傳輸的 NEON 媒體單元之間的直接介面。存儲的 L2 高速緩存設計,一次僅允許一個存儲體。對 L3 內存的多個未決事務的支持,以充分使用 CPU。 |

| TrustZone 技術 | 允許安全事務和數字版權管理 (DRM) |