Cortex-R4

2006年投放市場的處理器

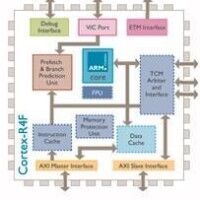

Cortex™-R4 處理器是第一個基於 ARMv7-R 體系結構的深層嵌入式實時處理器。

Cortex-R4 提供的性能、實時響應性大大高於同類中的其他處理器,它提供的功能也遠遠多於同類中的其他處理器。此處理器為 ASIC、ASSP 和 MCU 嵌入式應用提供出色的能效和成本效益。並且,可以在合成時配置 Cortex-R4 處理器以優化其功能集以便精確匹配應用需求。

Cortex-R4 是成熟的處理器,於 2006 年 5 月投放市場,如今已在數百萬的 ASIC、ASSP 和 MCU 設備中使用。它是高性能實時 SoC 的標準,取代了許多基於 ARM9 和 ARM11 處理器的設計。

Cortex-R4 是為基於 90 nm 至 28 nm 的高級晶元工藝的實現而設計的,此外其設計重點在於提升能效、實時響應性、高級功能和使得系統設計更加容易。基於 40 nm G 工藝,Cortex-R4 可以實現以將近 1 GHz 的頻率運行,此時它可提供 1,500 Dhrystone MIPS 的性能。該處理器提供高度靈活且有效的雙周期本地內存介面,使 SoC 設計者可以最大限度地降低系統成本和功耗。

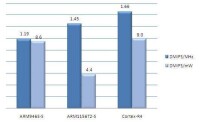

下圖對基於 90 nm G 工藝實現的 Cortex-R4 與經典 ARM 處理器的 Dhrystone 基準性能進行了比較。Cortex-R4 的配置選項可以進行選擇以最大限度地減少處理器的晶元面積,重要的是這還可以最大限度地降低漏泄功率。

Cortex-R4 性能更好、能效更高

Cortex-R4性能

Cortex-R4 與以前的 ARM9 和 ARM11 處理器相比具有其他許多顯著優勢:

| 內核 | ARM946E-S | ARM1156T2-S | Cortex-R4 |

| 體系結構 | ARMv5TE | ARMv6T2 | ARMv7-R |

| 預取單元 | 否 | 指令預取和分支預測 | |

| 超標量執行 | 否 | 雙執行指令 | |

| Thumb-2 指令 | 否 | 是 | |

| 浮點支持 | VFP9 | VFP11 | 已集成 (Cortex-R4F) |

| 匯流排介面 | AMBA AHB | AMBA3 AXI | |

| 緊密耦合內存 (TCM) | 基本 | 代碼和數據分離 | 完全靈活 |

| 中斷 | ARMv5 | ARMv6 增強功能、NMI | |

| 軟錯誤管理 | 否 | 針對所有 RAM 的可選奇偶校驗和 ECC | |

| 內存保護單元 (MPU) | 8 個區域 | 16 個區域 | 12 個區域 |

| 最小區域大小 | 4k 位元組 | 32 位元組,重疊區域 | |

| 合成可配置性 | 否 | I 和 D 高速緩存。0 或 2 個 TCM。軟錯誤處理。MPU | I 和 D 高速緩存。0、1、2 或 3 個 TCM。FPU。軟錯誤處理。MPU。AXI 從屬設備 |