轉譯後備緩衝區

TLB

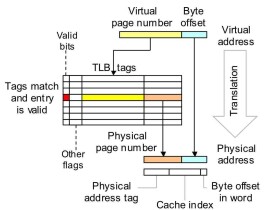

TLB(Translation Lookaside Buffer)轉換檢測緩衝區是一個內存管理單元,用於改進虛擬地址到物理地址轉換速度的緩存。

TLB是一個小的,虛擬定址的緩存,其中每一行都保存著一個由單個PTE(Page Table Entry,頁表項)組成的塊。如果沒有TLB,則每次取數據都需要兩次訪問內存,即查頁表獲得物理地址和取數據。

Translation Lookaside Buffer的縮寫,用於虛擬地址與實地址之間的交互,提供一個尋找實地址的緩存區,能夠有效減少尋找物理地址所消耗時間。

OLE庫文件,其中存放了OLE自動化對象的數據類型、模塊和介面定義,自動化伺服器通過TLB文件就能了解自動化對象的使用方法。

TLB:Translation lookaside buffer,即旁路轉換緩衝,或稱為頁表緩衝;裡面存放的是一些頁表文件(虛擬地址到物理地址的轉換表)。

又稱為快表技術。由於“頁表”存儲在主存儲器中,查詢頁表所付出的代價很大,由此產生了TLB。

X86保護模式下的定址方式:段式邏輯地址—〉線形地址—〉頁式地址;

頁式地址=頁面起始地址+頁內偏移地址;

對應於虛擬地址:叫page(頁面);對應於物理地址:叫frame(頁框);

X86體系的系統內存里存放了兩級頁表,第一級頁表稱為頁目錄,第二級稱為頁表。

TLB和CPU里的一級、二級緩存之間不存在本質的區別,只不過前者緩存頁表數據,而後兩個緩存實際數據。

1:TLB在X86體系的CPU里的實際應用最早是從Intel的486CPU開始的,在X86體系的CPU裡邊,一般都設有如下4組TLB:

第一組:緩存一般頁表(4K位元組頁面)的指令頁表緩存(Instruction-TLB);

第二組:緩存一般頁表(4K位元組頁面)的數據頁表緩存(Data-TLB);

第三組:緩存大尺寸頁表(2M/4M位元組頁面)的指令頁表緩存(Instruction-TLB);

第四組:緩存大尺寸頁表(2M/4M位元組頁面)的數據頁表緩存(Data-TLB);

2:TLB命中和TLB失敗

如果TLB中正好存放著所需的頁表,則稱為TLB命中(TLB Hit);如果TLB中沒有所需的頁表,則稱為TLB失敗(TLB Miss)。

3: TLB條目數 即TLB裡面可以存儲的表項數目,一般也叫entry數。

4:TLB的聯合方式

1〉全相聯方式:Athlon XP

2〉組相聯方式:P4

當CPU執行機構收到應用程序發來的虛擬地址后,首先到TLB中查找相應的頁表數據,如果TLB中正好存放著所需的頁表,則稱為TLB命中(TLB Hit),接下來CPU再依次看TLB中頁表所對應的物理內存地址中的數據是不是已經在一級、二級緩存里了,若沒有則到內存中取相應地址所存放的數據。既然說TLB是內存里存放的頁表的緩存,那麼它裡邊存放的數據實際上和內存頁表區的數據是一致的,在內存的頁表區里,每一條記錄虛擬頁面和物理頁框對應關係的記錄稱之為一個頁表條目(Entry),同樣地,在TLB裡邊也緩存了同樣大小的頁表條目(Entry)。