亞穩態

亞穩態

亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態引時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在這個穩定期間,觸發器輸出一些中間級電平,或者可能處于振盪狀態,並且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯式傳播下去。

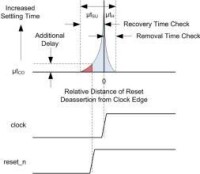

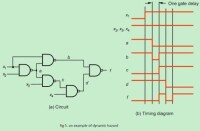

在同步系統中,如果觸發器的setup time / hold time不滿足,就可能產生亞穩態,此時觸發器輸出端Q在有效時鐘沿之後比較長的一段時間處於不確定的狀態,在這段時間裡Q端毛刺、振蕩、固定的某一電壓值,而不是等於數據輸入端D的值。這段時間稱為決斷時間(resolution time)。經過resolution time之後Q端將穩定到0或1上,但是究竟是0還是1,是隨機的,與輸入沒有必然的關係。

亞穩態

(1)細晶組織 當組織細小時,界面增多,自由能升高,故為亞穩狀態。

(2)高密度晶體缺陷的存在 晶體缺陷使原子偏離平衡位置,晶體結構排列的規則性下降,故體系自由能增高。

(3)形成過飽和固溶體 即溶質原子在固溶體中的濃度超過平衡濃度,甚至在平衡狀態是互不溶解的組元發生了相互溶解。

(5)由晶態轉變為非晶態,由結構有序變為結構無序,自由能增高。

1 降低系統時鐘

2 用反應更快的FF

3 引入同步機制,防止亞穩態傳播

4 改善時鐘質量,用邊沿變化快速的時鐘信號

關鍵是器件使用比較好的工藝和時鐘周期的裕量要大。

亞穩態

只要系統中有非同步元件,亞穩態就是無法避免的,因此設計的電路首先要減少亞穩態導致錯誤的發生,其次要使系統對產生的錯誤不敏感。前者要用同步電路來實現,而後者根據不同的設計應用有不同的處理辦法。左邊為非同步輸入端,經過兩級觸發器同步,在右邊的輸出將是同步的,而且該輸出基本不存在亞穩態。其原理是即使第一個觸發器的輸出端存在亞穩態,經過一個CLK周期后,第二個觸發器D端的電平仍未穩定的概率非常小,因此第二個觸發器Q端基本不會產生亞穩態。

注意,這裡說的是“基本”,也就是無法“根除”,那麼如果第二個觸發器Q出現了亞穩態會有什麼後果呢?後果的嚴重程度是由你的設計決定的,如果系統對產生的錯誤不敏感,那麼系統可能正常工作,或者經過短暫的異常之後可以恢復正常工作,例如設計非同步FIFO時使用格雷碼計數器當讀寫地址的指針就是處於這方面的考慮。如果設計上沒有考慮如何降低系統對亞穩態的敏感程度,那麼一旦出現亞穩態,系統可能就崩潰了。

使用同步電路以後,亞穩態仍然有發生的可能,與此相連的是MTBF(Mean Time Between Failure),亞穩態的發生概率與時鐘頻率無關,但是MTBF與時鐘有密切關係。有文章提供了一個例子,某一系統在20MHz時鐘下工作時,MTBF約為50年,但是時鐘頻率提高到40MHz時,MTBF只有1分鐘!可見降低時鐘頻率可以大大減小亞穩態導致系統錯誤的出現,其原因在於,提供較長的resolution time可減小亞穩態傳遞到下一級的機會,提高系統的MTBF。