74LS373

74LS373

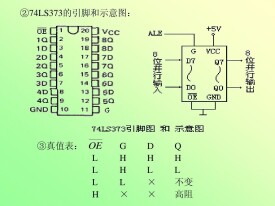

7徠4LS373是三態輸出的八D鎖存器,共有54S373和74LS373兩種線路。373 的輸出端 Q0~Q7 可直接與匯流排相連。

當鎖存允許端LE為高電平時,Q 隨數據D而變。當LE為低電平時,D 被鎖存在已建立的數據電平。當LE端施密特觸發器的輸入滯後作用,使交流和直流雜訊抗擾度被改 400mV。

結構型式,其主要電氣特性的典型值如下(不同廠傢具體值有差別):

74ls373的照片及內部結構

54S373/74S373 7ns 525mW

54LS373/74LS373 17ns 120mW

當三態允許控制端 OE 為低電平時,Q0~Q7為正常邏輯狀態,可用來驅動負載或匯流排。當 OE 為高電平時,Q0~Q7 呈高阻態,既不驅動匯流排,也不為匯流排的負載,但鎖存器內部的邏輯操作不受影響。

D0~D7 數據輸入端

徠OE 三態允許控制端(低電平有效)

Q0~Q7 輸出端

| Dn | LE | OE | Qn |

| H | H | L | H |

| L | H | L | L |

| X | L | L | Q0 |

| X | X | H | 高阻態 |