非同步計數器

非同步計數器

異徠步計數器是非同步時序電路,其主要特點是內部各觸發器的時鐘脈衝端CP不全都連接在一起,因此各觸發器的翻轉時刻有先有后,其輸出可能會產生干擾毛刺現象,但其電路結構簡單。

非同步二進位計數器在做加法計數時是以從低位到高位逐位進位的方式T作的。因此,其中的各個觸發器不是同步翻轉的。按照二進位加法計數規則,第i位如果為1,則再加上1時應變為0,同時向高位發出進位信號,使高位翻轉。若使用T'觸發器構成計數器電路,則只需將低位觸發器的Q(或Q)端接至高位觸發器的時鐘輸入端即可實現進位。當低位由1變為0時,Q端的下降沿正好可以作為高位的時鐘信號(若採用下降沿觸發的T'觸發器),或者Q端的上升沿作為高位的時鐘信號(若採用上升沿觸發的T'觸發器)。

按照二進位減法計數規則,若低位觸發器已經為0,則再輸入一個減法計數脈衝后應翻轉為1,同時向高位發出借位信號,使高位翻轉。若使用T’觸發器構成計數器電路,則只需將低位觸發器的Q(或Q)端接至高位觸發器的時鐘輸入端即可實現進位。當低位由0變為1時,Q端的下降沿正好可以作為高位的時鐘信號(若採用下降沿觸發的T’觸發器),或者Q端的上升沿作為高位的時鐘信號(若採用上升沿觸發的T’觸發器)。

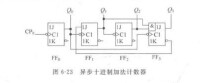

非同步十進位加法計數器是在4位非同步二進位加法計數器的基礎上得到的,如圖1所示。修改時主要解決的問題是如何使4位二進位計數器在計數過程中跳過1010~1111這6個狀態。假定所選用的觸發器都是TTL,電路J、K懸空時相當於邏輯1電平。

圖1

當第徠8個計數脈衝輸入時(此時計數器的狀態為QQQQ-0111),由於J=K=1,所以Q的下降沿到達后Q由0變為1。同時J也隨著Q變為0。第9個計數脈衝輸入以後,電路狀態變為QQQQ-1001。第10個計數脈衝輸入后,觸發器FF翻轉成0,同時Q的下降沿使觸發器FF置0,於是電路從1001返回到0000,跳過了1010~1111這6個狀態,成為十進位計數器。

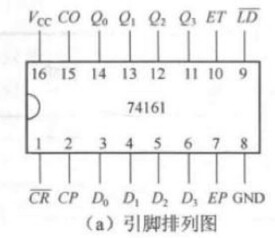

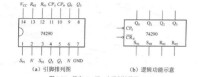

圖2所示為非同步二一五一十進位計數器74290的引腳排列圖和邏輯功能示意圖。它由三個JK型觸發器、一個RS型觸發器及幾個附加門組成。R和R為非同步清零端:S和S為非同步置9端。整個電路可看作由兩個獨立的計數器組成。計數器I是由一個觸發器構成的一位二進位計數器,其時鐘脈衝端為CP,狀態輸出端為Q;計數器II是由三個觸發器構成的五進位非同步計數器,它的時鐘脈衝端為CP,狀態輸出端為QQQ。

圖2