cD4046是通用的CMOS鎖相環集成電路,其特點是電源電壓範圍寬(為3V-18V),輸入阻抗高(約100MΩ),動態功耗小,在中心頻率f0為10kHz下功耗僅為600μW,屬微功耗器件。

cd4046

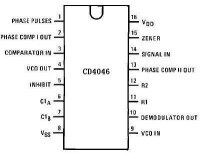

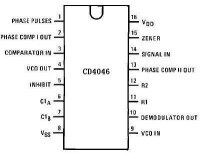

CD4046引腳功能

CD4046的引腳排列,採用16腳雙列直插式,各管腳功能:

1腳相位輸出端,環路入鎖時為高電平,環路失鎖時為

低電平。

2腳相位比較器Ⅰ的輸出端。

3腳比較信號輸入端。

5腳禁止端,高電平時禁止,低電平時允許壓控振蕩器工作。

6、7腳外接振蕩電容。

8、16腳電源的負端和正端。

9腳壓控振蕩器的控制端。

10腳解調輸出端,用於FM解調。

11、12腳外接振蕩電阻。

13腳相位比較器Ⅱ的輸出端。

14腳信號輸入端。

15腳內部獨立的齊納穩壓管負極。

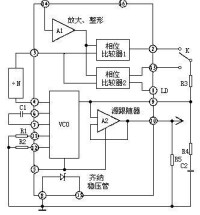

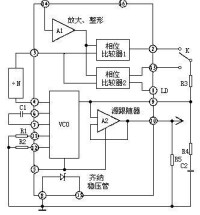

圖3

圖3是CD4046內部電路原理框圖,主要由相位比較Ⅰ、Ⅱ、壓控振蕩器(VCO)、線性放大器、源跟隨器、整形電路等部分構成。

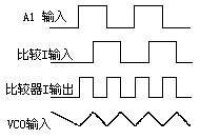

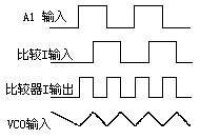

比較器Ⅰ採用異或門結構,當兩個輸入端信號Ui、Uo的電平狀態相異時(即一個高電平,一個為低電平),輸出端信號UΨ為高電平;反之,Ui、Uo電平狀態相同時(即兩個均為高,或均為低電平),UΨ輸出為低電平。當Ui、Uo的相位差Δφ在0°-180°範圍內變化時,UΨ的脈衝寬度m亦隨之改變,即占空比亦在改變。從比較器Ⅰ的輸入和輸出信號的波形(如圖4所示)可知,其輸出信號的頻率等於輸入信號頻率的兩倍,並且與兩個輸入信號之間的中心頻率保持90°相移。從圖中還可知,fout不一定是對稱波形。對相位比較器Ⅰ,它要求Ui、Uo的占空比均為50%(即

方波),這樣才能使鎖定範圍為最大。

相位比較器Ⅱ是一個由信號的上升沿控制的數字存儲網路。它對輸入信號占空比的要求不高,允許輸入非對稱波形,它具有很寬的捕捉頻率範圍,而且不會鎖定在輸入信號的諧波。它提供數字誤差信號和鎖定信號(相位脈衝)兩種輸出,當達到鎖定時,在相位比較器Ⅱ的兩個輸人信號之間保持0°相移。

圖4

對相位比較器Ⅱ而言,當14腳的輸入信號比3腳的比較信號頻率低時,輸出為邏 輯“0”;反之則輸出邏輯“1”。如果兩信號的頻率相同而相位不同,當輸入信號的相位滯後於比較信號時,相位比較器Ⅱ輸出的為正脈衝,當相位超前時則輸出為負脈衝。在這兩種情況下,從1腳都有與上述正、負脈衝寬度相同的負脈衝產生。從相位比較器Ⅱ輸出的正、負脈衝的寬度均等於兩個輸入脈衝上升沿之間的相位差。而當兩個輸入脈衝的頻率和相位均相同時,相位比較器Ⅱ的輸出為高阻態,則1腳輸出高電平。上述波形如圖5所示。由此可見,從1腳輸出信號是負脈衝還是固定高電平就可以判斷兩個輸入信號的情況了

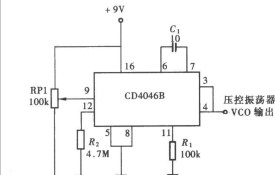

CD4046鎖相環採用的是RC型壓控振蕩器,必須外接

電容C1和電阻R1作為充放電元件。當PLL對跟蹤的輸入信號的頻率寬度有要求時還需要外接電阻R2。由於VCO是一個電壓控制振蕩器,對定時電容C1的充電電流與從9腳輸入的控制電壓成正比,使VCO的振蕩頻率亦正比於該控制電壓。當VCO控制電壓為0時,其輸出頻率最低;當輸入控制電壓等於電源電壓VDD時,輸出頻率則線性地增大到最高輸出頻率。VCO振蕩頻率的範圍由R1、R2和C1決定。由於它的充電和放電都由同一個電容C1完成,故它的輸出波形是對稱方波。一般規定CD4046的最高頻率為1.2MHz(VDD=15V),若VDD<15V,則fmax要降低一些。

輸入信號 Ui從14腳輸入后,經放大器A1進行放大、整形后加到相位比較器Ⅰ、Ⅱ的輸入端,圖3開關K撥至2腳,則比較器Ⅰ將從3腳輸入的比較信號Uo與輸入信號Ui作相位比較,從相位比較器輸出的誤差電壓UΨ則反映出兩者的相位差。UΨ經R3、R4及C2濾波后得到一控制電壓Ud加至壓控振蕩器VCO的輸入端9腳,調整VCO的振蕩頻率f2,使f2迅速逼近信號頻率f1。VCO的輸出又經除法器再進入相位比較器Ⅰ,繼續與Ui進行相位比較,最後使得f2=f1,兩者的相位差為一定值,實現了相位鎖定。若開關K撥至13腳,則相位比較器Ⅱ工作,過程與上述相同,不再贅述。

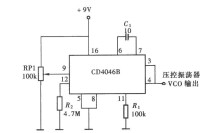

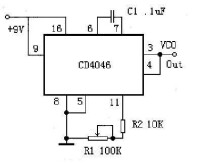

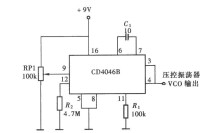

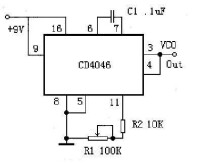

用CD4046的VCO組成的方波發生器電路圖

圖6是用CD4046的VCO組成的方波發生器,當其9腳輸入端固定接電源時,電路即起基本方波振蕩器的作 用。

振蕩器的充、放電電容C1接在6腳與7腳之間,調節電阻R1阻值即可調整振蕩器振蕩頻率,振蕩

方波信號從4腳輸出。按圖示數值,振蕩頻率變化範圍在20Hz至2kHz。

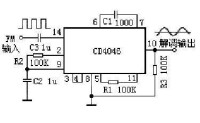

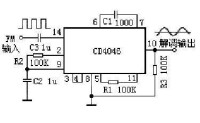

CD4046鎖相環用於調頻信號的解調電路

圖7是CD4046鎖相環用於調頻信號的解調電路。如果由載頻為10kHz組成的調頻信號,用400Hz音頻信號調製,假如調頻信號的總振幅小於400mV時,用CD4046時則應經放大器放大後用交流耦合到

鎖相環的14腳輸入端環路的相位比較器採用比較器Ⅰ,因為需要鎖相環系統中的中心頻率f0等於調頻信號的載頻,這樣會引起壓控振蕩器輸出與輸入信號輸入間產生不同的相位差,從而在壓控振蕩器輸入端產生與輸入信號頻率變化相應的電壓變化,這個電壓變化經源跟隨器隔離后在壓控振蕩器的解調輸出端10腳輸出解調信號。當VDD為10V,R1為10kΩ,C1為100pF時,鎖相環路的捕捉範圍為±0.4kHz。解調器輸出幅度取決於源跟隨器外接電阻R3值的大小。

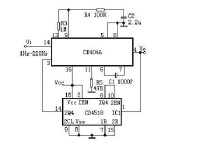

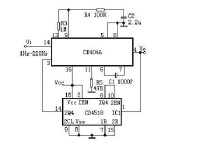

100倍頻電路

圖8用CD4046與BCD加法計數器CD4518構成的100倍頻電路。剛開機時,f2可能不等於f1,假定f2

U0,則相位比較器Ⅱ輸出UΨ為低電平。UΨ經濾波后得到的Ud信號開始下降,這就迫使VCO對f2進行微調,最後達到f2/N=f1,並且f2與f1的相位差Δφ=0°。,進入鎖定狀態。如果此後f1又發生變化,鎖相環能再次捕獲f1,使f2與f1相位鎖定。