複位電路

複位電路

複位電路是一種用來使電路恢復到起始狀態的電路設備,它的操作原理與計算器有著異曲同工之妙,只是啟動原理和手段有所不同。複位電路,就是利用它把電路恢復到起始狀態。就像計算器的清零按鈕的作用一樣,以便回到原始狀態,重新進行計算。

和計算器清零按鈕有所不同的是,複位電路啟動的手段有所不同。一是在給電路通電時馬上進行複位操作;二是在必要時可以由手動操作;三是根據程序或者電路運行的需要自動地進行。複位電路都是比較簡單的大都是只有電阻和電容組合就可以辦到了,再複雜點就有三極體等配合程序來進行了。

為確保微機系統中電路穩定可靠工作,複位電路是必不可少的一部分,複位電路的第一功能是上電複位。一般微機電路正常工作需要供電電源為5V±5%,即4.75~5.25V。由於微機電路是時序數字電路,它需要穩定的時鐘信號,因此在電源上電時,只有當VCC超過4.75V低於5.25V以及晶體振蕩器穩定工作時,複位信號才會撤除,微機電路開始正常工作。

如果主板上沒有ISA匯流排,也就是8XX系列晶元組的主板,IDE的複位直接來自於南橋,在兩者之間通常也會有一個非門或是反向電子開關,PCI匯流排的複位直接來自於南橋,有些主板會在兩者之間加有跟隨器,此跟隨器起緩衝延時作用。且PCI的常態為3.3V 或5V,複位時為0V,AGP匯流排的複位信號和PCI匯流排的複位信號是同路產生。也有的主板AGP匯流排的複位也是由南橋直接供給,常態時為高電頻,複位時為低電頻,對於北橋的複位信號也是和PCI匯流排的複位信號同時產生,也就是說PCI匯流排的複位信號,AGP匯流排的複位信號和北橋的複位信號通常是串在一根線上的,複位信號都相同,對於CPU的複位信號,不同的主板都是由北橋供給,I/O的複位信號是由南橋直接供給,通常是3.3V或5V。在8XX系列晶元組的主板中,固件中心(B205)和時鐘發生器晶元也有複位信號,且複位信號由南橋直接供給,常態為3.3V,複位時為0V。

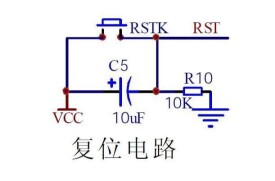

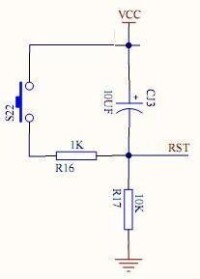

複位電路工作原理如右圖所示,VCC上電時,使電容C充電,在10K電阻上出現高電位電壓,使得單片機複位;幾個毫秒后,C充滿,10K電阻上電流降為0,電壓也為0,使得單片機進入工作狀態。工作期間,按下S22,C放電,放電結束后,在10K電阻上出現電壓,使得單片機進入複位狀態,直到

複位電路

單片機在啟動時都需要複位,以使CPU及系統各部件處於確定的初始狀態,並從初態開始工作。89系列單片機的複位信號是從RST引腳輸入到晶元內的施密特觸發器中的。當系統處於正常工作狀態時,且振蕩器穩定后,如果RST引腳上有一個高電平並維持2個機器周期(24個振蕩周期)以上,則CPU就可以響應並將系統複位。單片機系統的複位方式有:手動按鈕複位和上電複位。

1、手動按鈕複位

手動按鈕複位需要人為在複位輸入端RST上加入高電平(圖1)。一般採用的辦法是在RST端和正電源Vcc之間接一個按鈕。當人為按下按鈕時,則Vcc的+5V電平就會直接加到RST端。手動按鈕複位的電路如所示。由於人的動作再快也會使按鈕保持接通達數十毫秒,所以,完全能夠滿足複位的時間要求。

2、上電複位

AT89C51的上電複位電路如圖2所示,只要在RST複位輸入引腳上接一電容至Vcc端,下接一個電阻到地即可。對於CMOS型單片機,由於在RST端內部有一個下拉電阻,故可將外部電阻去掉,而將外接電容減至1uF。上電複位的工作過程是在加電時,複位電路通過電 容加給RST端一個短暫的高電平信號,此高電平信號隨著Vcc對電容的充電過程而逐漸回落,即RST端的高電平持續時間取決於電容的充電時間。為了保證系統能夠可靠地複位,RST端的高電平信號必須維持足夠長的時間。上電時,Vcc的上升時間約為10ms,而振蕩器的起振時間取決于振盪頻率,如晶振頻率為10MHz,起振時間為1ms;晶振頻率為1MHz,起振時間則為10ms。在圖2的複位電路中,當Vcc掉電時,必然會使RST端電壓迅速下降到0V以下,但是,由於內部電路的限制作用,這個負電壓將不會對器件產生損害。另外,在複位期間,埠引腳處於隨機狀態,複位后,系統將埠置為全“l”態。如果系統在上電時得不到有效的複位,則程序計數器PC將得不到一個合適的初值,因此,CPU可能會從一個未被定義的位置開始執行程序。

3、積分型上電複位

常用的上電或開關複位電路如圖3所示。上電后,由於電容C3的充電和反相門的作用,使RST持續一段時間的高電平。當單片機已在運行當中時,按下複位鍵K后鬆開,也能使RST為一段時間的高電平,從而實現上電或開關複位的操作。

根據實際操作的經驗,下面給出這種複位電路的電容、電阻參考值。

C=1uF,Rl=lk,R2=10k

單片機複位電路主要有四種類型:

(1)微分型複位電路。

(2)積分型複位電路。

(3)比較器型複位電路。

(4)看門狗型複位電路。

看門狗型複位電路主要利用CPU正常工作時,定時複位計數器,使得計數器的值不超過某一設定的值;當CPU不能正常工作時,由於計數器不能被複位,因此其計數會超過某一值,從而產生複位脈衝,使得CPU恢復正常工作狀態。此複位電路的可靠性主要取決於軟體設計,即將定時向複位電路發出脈衝的程序放在何處是最優的設計。一般設計,將此段程序放在定時器中斷服務子程序中。然而,有時這種設計仍然會引起程序走飛或工作不正常。原因主要是:當程序"走飛"發生時,定時器初始化以及開中斷之後的話,這種"走飛"情況就有可能不能由Watchdog複位電路校正回來。因為定時器中斷一真在產生,即使程序不正常,Watchdog也能被正常複位。為此提出定時器加預設的設計方法。即在初始化時壓入堆棧一個地址,在此地址內執行的是一條關中斷和一條死循環語句。在所有不被程序代碼佔用的地址儘可能地用子程序返回指令RET代替。這樣,當程序走飛后,其進入陷阱的可能性將大大增加。而一旦進入陷阱,定時器停止工作並且關閉中斷,從而使Watchdog複位電路會產生一個複位脈衝將CPU複位。當然這種技術用於實時性較強的控制或處理軟體中有一定的困難。

比較器型複位電路的基本原理。上電複位時,由於組成了一個RC低通網路,所以比較器的正相輸入端的電壓比負相端輸入電壓延遲一定時間。而比較器的負相端網路的時間常數遠遠小於正相端RC網路的時間常數,因此在正端電壓還沒有超過負端電壓時,比較器輸出低電平,經反相器后產生高電平。複位脈衝的寬度主要取決於正常電壓上升的速度。由於負端電壓放電迴路時間常數較大,因此對電源電壓的波動不敏感。但是容易產生以下二種不利現象:

(1)電源二次開關間隔太短時,複位不可靠。

(2)當電源電壓中有浪涌現象時,可能在浪涌消失后不能產生複位脈衝。

為此,將改進比較器重定電路,如圖9所示。這個改進電路可以消除第一種現象,並減少第二種現象的產生。為了徹底消除這二種現象,可以利用數字邏輯的方法和比較器配合,設計的比較器重定電路。此電路稍加改進即可作為上電複位和看門狗複位電路共同複位的電路,大大提高了複位的可靠性。