邏輯地址

邏輯地址

邏輯地址所屬現代詞,指的是把用戶程序中使用的地址稱為相對地址。段標識符是由一個16位長的欄位組成,稱為段選擇符。這個東東就是“段描述符(segment descriptor)”,呵呵,段描述符具體地址描述了一個段(對於“段”這個字眼的理解:我是把它想像成,拿了一把刀,把虛擬內存,砍成若干的截——段。Intel設計的本意是,一些全局的段描述符,就放在“全局段描述符表(GDT)”中,一些局部的,例如每個進程自己的,就放在所謂的“局部段描述符表(LDT)”中。

"邏輯址" 照

; ;

、址換功計算,訪指令址 (操) 邏輯址,址。定址式計算換存儲器址。

2、把用戶程序中使用的地址稱為相對地址即邏輯地址。

3、邏輯地址由兩個16位的地址分量構成,一個為段基值,另一個為偏移量。兩個分量均為無符號數編碼。

1、這樣該存儲單元的地址就可以用段基址(段地址)和段內偏移量(偏移地址)來表示,段基址確定它所在的段居於整個存儲空間的位置,偏移量確定它在段內的位置,這種地址表示方式稱為邏輯地址,通常表示為段地址:偏移地址的形式。

2、所謂邏輯地址是指按數據的邏輯塊號給出的磁碟的位置()而物理地址則是由磁碟的柱面、頭、段等物理位置所確定的地址。

追根求源,Intel的8位機8080CPU,數據匯流排(DB)為8位,地址匯流排(AB)為16位。那麼這個16位地址信息也是要通過8位數據匯流排來傳送,也是要在數據通道中的暫存器,以及在CPU中的寄存器和內存中存放的,但由於AB正好是DB的整數倍,故不會產生矛盾!

但當上升到16位機后,Intel8086/8088CPU的設計由於當年IC集成技術和外封裝及引腳技術的限制,不能超過40個引腳。但又感覺到8位機原來的地址定址能力太少了,但直接增加到16的整數倍即令位又是達不到的。故而只能把AB暫時增加4條成為20條。則的定址能力已經增加了16倍。但此舉卻造成了AB的20位和DB的16位之間的矛盾,20位地址信息既無法在DB上傳送,又無法在16位的CPU寄存器和內存單元中存放。於是應運而生就產生了CPU段結構的原理。

一個邏輯地址由兩部份組成,段標識符: 段內偏移量。段標識符是由一個16位長的欄位組成,稱為段選擇符。其中前13位是一個索引號。後面3位包含一些硬體細節,如圖:

邏輯地址

邏輯地址

Intel設計的本意是,一些全局的段描述符,就放在“全局段描述符表()”中,一些局部的,例如每個進程自己的,就放在所謂的“局部段描述符表()”中。那究竟什麼時候該用,什麼時候該用呢?這是由段選擇符中的T1欄位表示的,,表示用,表示用。

在內存中的地址和大小存放在CPU的gdtr控制寄存器中,而LDT則在ldtr寄存器中。

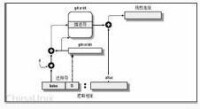

好多概念,像繞口令一樣。這張圖看起來要直觀些:

邏輯地址

1、看段選擇符的還是1,知道當前要轉換是GDT中的段,還是LDT中的段,再根據相應寄存器,得到其地址和大小。我們就有了一個數組了。

2、拿出段選擇符中前13位,可以在這個數組中,查找到對應的段描述符,這樣,它了Base,即基地址就知道了。

3、把,就是要轉換的線性地址了。