寄存器

中央處理器內的組成部分

寄存器的功能是存儲二進位代碼,它是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲1位二進位代碼,故存放n位二進位代碼的寄存器,需用n個觸發器來構成。

按照功能的不同,可將寄存器分為基本寄存器和移位寄存器兩大類。基本寄存器只能并行送入數據,也只能并行輸出。移位寄存器中的數據可以在移位脈衝作用下依次逐位右移或左移,數據既可以并行輸入、并行輸出,也可以串列輸入、串列輸出,還可以并行輸入、串列輸出,或串列輸入、并行輸出,十分靈活,用途也很廣。

寄存器,是集成電路中非常重要的一種存儲單元,通常由觸發器組成。在集成電路設計中,寄存器可分為電路內部使用的寄存器和充當內外部介面的寄存器這兩類。內部寄存器不能被外部電路或軟體訪問,只是為內部電路的實現存儲功能或滿足電路的時序要求。而介面寄存器可以同時被內部電路和外部電路或軟體訪問,CPU中的寄存器就是其中一種,作為軟硬體的介面,為廣泛的通用編程用戶所熟知。

在計算機領域,寄存器是CPU內部的元件,包括通用寄存器、專用寄存器和控制寄存器。寄存器擁有非常高的讀寫速度,所以在寄存器之間的數據傳送非常快。

寄存器是內存階層中的最頂端,也是系統獲得操作資料的最快速途徑。寄存器通常都是以他們可以保存的位元數量來估量,

寄存器

寄存器通常都用來意指由一個指令之輸出或輸入可以直接索引到的暫存器群組。更適當的是稱他們為“架構寄存器”。

寄存器最起碼具備以下4種功能。

①清除數碼:將寄存器里的原有數碼清除。

②接收數碼:在接收脈衝作用下,將外輸入數碼存入寄存器中。

③存儲數碼:在沒有新的寫入脈衝來之前,寄存器能保存原有數碼不變。

④輸出數碼:在輸出脈衝作用下,才通過電路輸出數碼。

具有以上功能的寄存器稱為數碼寄存器;有的寄存器還具有移位功能,稱為移位寄存器。

寄存器有串列和并行兩種數碼存取方式。將n位二進位數一次存入寄存器或從寄存器中讀出的方式稱為并行方式。將n位二進位數以每次1位,分成n次存入寄存器並從寄存器讀出,這種方式稱為串列方式。并行方式只需一個時鐘脈衝就可以完成數據操作,工作速度快,但需要n根輸入和輸出數據線。串列方式要使用幾個時鐘脈衝完成輸入或輸出操作,工作速度慢,但只需要一根輸入或輸出數據線,傳輸線少,適用於遠距離傳輸。

寄存器

在數字電路中,用來存放二進位數據或代碼的電路稱為寄存器。寄存器是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲1位二進位代碼,存放門位二進位代碼的寄存器需用逐個觸發器來構成。

對寄存器中的觸發器只要求它們具有置1,置0的功能即可,因而無論是用電平觸發的觸發器,還是用脈衝觸發或邊沿觸發的觸發器,都可以組成寄存器。

由電平觸發的動作特點可知,在CLK高電平期間,Q端的狀態跟隨D端狀態的改變而改變;CLK變成低電平以後,Q端將保持CLK變為低電平時刻D端的狀態。

74HC175則是用CMOS邊沿觸發器組成的4位寄存器,根據邊沿觸發的動作特點可知,觸發器輸出端的狀態僅僅取決於CLK上升沿到達時刻D端的狀態。可見,雖然74LS75和74HC175都是4位寄存器,但由於採用了不同結構類型的觸發器,所以動作特點是不同的。

為了增加使用的靈活性,在有些寄存器電路中還附加了一些控制電路,使寄存器又增添了非同步置零、輸出三態控制和保持等功能。這裡所說的保持,是指CLK信號到達時觸發器不隨D端的輸入信號而改變狀態,保持原來的狀態不變。

上面介紹的兩個寄存器電路中,接收數據時所有各位代碼都是同時輸入的,而且觸發器中的數據是并行地出現在輸出端的,因此將這種輸入、輸出方式稱為并行輸入、并行輸出方式。

1.通用寄存器組

通用寄存器組包括AX、BX、CX、DX4個16位寄存器,用以存放16位數據或地址。也可用作8位寄存器。用作8位寄存器時分別記為AH、AL、BH、BL、CH、CL、DH、DL。只能存放8位數據,不能存放地址。它們分別是AX、BX、CX、DX的高八位和低八位。若AX=1234H,則AH=12H,AL=34H。通用寄存器通用性強,對任何指令,它們具有相同的功能。為了縮短指令代碼的長度,在8086中,某些通用寄存器用作專門用途。例如,串指令中必須用CX寄存器作為計數寄存器,存放串的長度,這樣在串操作指令中不必給定CX的寄存器號,縮短了串操作指令代碼的長度。下面一一介紹:

AX(AH、AL):累加器。有些指令約定以AX(或AL)為源或目的寄存器。輸入/輸出指令必須通過AX或AL實現,例如:埠地址為43H的內容輸入CPU的指令為INAL,43H或INAX,43H。目的操作數只能是AL/AX,而不能是其他的寄存器。

BX(BH、BL):基址寄存器。BX可用作間接定址的地址寄存器和基地址寄存器,BH、BL可用作8位通用數據寄存器。

CX(CH、CL):計數寄存器。CX在循環和串操作中充當計數器,指令執行后CX內容自動修改,因此稱為計數寄存器。

DX(DH、DL):數據寄存器。除用作通用寄存器外,在I/O指令中可用作埠地址寄存器,乘除指令中用作輔助累加器。

2.指針和變址寄存器

BP( Base Pointer regilter):基址指針寄存器。

SP( Stack Pointer Register):堆棧指針寄存器。

SI( Source Index register):源變址寄存器。

DI( Destination Index Register):目的變址寄存器。

這組寄存器存放的內容是某一段內地址偏移量,用來形成操作數地址,主要在堆棧操作和變址運算中使用。BP和SP寄存器稱為指針寄存器,與SS聯用,為訪問現行堆棧段提供方便。通常BP寄存器在間接定址中使用,操作數在堆棧段中,由SS段寄存器與BP組合形成操作數地址即BP中存放現行堆棧段中一個數據區的“基址”的偏移量,所以稱BP寄存器為基址指針。

SP寄存器在堆棧操作中使用,PUSH和POP指令是從SP寄存器得到現行堆棧段的段內地址偏移量,所以稱SP寄存器為堆棧指針,SP始終指向棧頂。

寄存器SI和DI稱為變址寄存器,通常與DS一起使用,為訪問現行數據段提供段內地址偏移量。在串指令中,其中源操作數的偏移量存放在SⅠ中,目的操作數的偏移量存放在DI中,SI和DI的作用不能互換,否則傳送地址相反。在串指令中,SI、DI均為隱含定址,此時,SI和DS聯用,Dl和ES聯用。

3.段寄存器

8086/8088CPU可直接定址1MB的存儲器空間,直接定址需要20位地址碼,而所有內部寄存器都是16位的,只能直接定址6KB,因此採用分段技術來解決。將1MB的存儲空間分成若干邏輯段,每段最長64KB,這些邏輯段在整個存儲空間中可浮動。

8086/8088CPU內部設置了4個16位段寄存器,它們分別是代碼段寄存器CS、數據段寄存器DS、堆棧段寄存器SS、附加段寄存器ES、由它們給出相應邏輯段的首地址,稱為“段基址”。段基址與段內偏移地址組合形成20位物理地址,段內偏移地址可以存放在寄存器中,也可以存放在存儲器中。

例如:代碼段寄存器CS存放當前代碼段基地址,IP指令指針寄存器存放了下一條要執行指令的段內偏移地址,其中CS=2000H,IP=001AH。通過組合,形成20位存儲單元的定址地址為2001AH。

代碼段內存放可執行的指令代碼,數據段和附加段內存放操作的數據,通常操作數在現行數據段中,而在串指令中,目的操作數指明必須在現行附加段中。堆棧段開闢為程序執行中所要用的堆棧區,採用先進後出的方式訪問它。各個段寄存器指明了一個規定的現行段,各段寄存器不可互換使用。程序較小時,代碼段、數據段、堆棧段可放在一個段內,即包含在64KB之內,而當程序或數據量較大時,超過了64KB,那麼可以定義多個代碼段或數據段、堆棧段、附加段。現行段由段寄存器指明段地址,使用中可以修改段寄存器內容,指向其他段。有時為了明確起見,可在指令前加上段超越的前綴,以指定操作數所在段。

4.指令指針寄存器IP

8086/8088CPU中設置了一個16位指令指針寄存器IP,用來存放將要執行的下一條指令在現行代碼段中的偏移地址。程序運行中,它由BIU自動修改,使IP始終指向下一條將要執行的指令的地址,因此它是用來控制指令序列的執行流程的,是一個重要的寄存器。8086程序不能直接訪問IP,但可以通過某些指令修改IP的內容。例如,當遇到中斷指令或調用子程序指令時,8086自動調整IP的內容,將IP中下一條將要執行的指令地址偏移量入棧保護,待中斷程序執行完畢或子程序返回時,可將保護的內容從堆棧中彈出到IP,使主程序繼續運行。在跳轉指令時,則將新的跳轉目標地址送入IP,改變它的內容,實現了程序的轉移。

5.標誌寄存器FR

標誌寄存器FR也稱程序狀態字寄存器。

FR是16位寄存器,其中有9位有效位用來存放狀態標誌和控制標誌。狀態標誌共6位,CF、PF、AF、ZF、SF和OF,用於寄存程序運行的狀態信息,這些標誌往往用作後續指令判斷的依據。控制標誌有3位,IF、DF和TF,用於控制CPU的操作,是人為設置的。

寄存器

在計算機及其他計算系統中,寄存器是一種非常重要的、必不可少的數字電路課件,它通常由觸發器(D觸發器)組成,主要作用是用來暫時存放數碼或指令。一個觸發器可以存放一位二進位代碼,若要存放N位二進位數碼,則需用N個觸發器。

寄存器應具有接收數據、存放數據和輸出數據的功能,它由觸發器和門電路組成。只有得到“存入脈衝”(又稱“存入指令”、“寫入指令”)時,寄存器才能接收數據;在得到“讀出”指令時,寄存器才將數據輸出。

寄存器存放數碼的方式有并行和串列兩種。并行方式是數碼從各對應位輸入端同時輸入到寄存器中;串列方式是數碼從一個輸入端逐位輸入到寄存器中。

寄存器讀出數碼的方式也有并行和串列兩種。在并行方式中,被讀出的數碼同時出現在各位的輸出端上;在串列方式中,被讀出的數碼在一個輸出端逐位出現。

(1)代碼要存得進;

(2)代碼要記得住;

(3)代碼要取得出。

寄存器是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲1位2進位代碼,存放n位2進位代碼的寄存器,需用n個觸發器來構成。對寄存器中的觸發器只要求它具有置1、置0的功能即可,因而無論用何種類型的觸發器都可組成寄存器。

按照功能的不同,寄存器可分為基本寄存器和移位寄存器兩大類。基本寄存器只能并行送入數據,需要時也只能并行輸出。

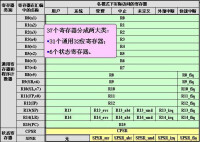

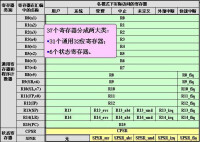

ARM微處理器共有37個32位寄存器,其中31個為通用寄存器,6個為狀態寄存器。但是這些寄存器不能被同時訪問,具體哪些寄存器是可編程訪問的,取決於微處理器的工作狀態及具體的運行模式。但在任何時候,通用寄存器R14~R0、程序計數器PC、一個或兩個狀態寄存器都是可訪問的。

ARM9處理器共有37個32位長的寄存器,這些寄存器包括:

(1) RO~R12:均為32位通用寄存器,用於數據操作。但是注意:絕大多數16位Thumb指令只能訪問R0~R7,而32位Thumb -2指令可以訪問所有寄存器。

(2)堆棧指針:堆棧指針的最低兩位永遠是O,這意味著堆棧總是4位元組對齊的。

(3)鏈接寄存器:當呼叫一個子程序時,由R14存儲返回地址。

(4)程序計數器:指向當前的程序地址,如果修改它的值,就能改變程序的執行流。

(5)6個狀態寄存器(1個CPSR、5個SPSR),用以標識CPU的工作狀態及程序的運行狀態,均為32位,目前只使用了其中的一部分。

Cortex-A8處理器有40個32位長的寄存器,多了監控模式下的寄存器,如RO~R12、R15、CPSR通用,R13_ mon、R14_mon、SPSR_mon三個專用寄存器。

寄存器定址就是利用寄存器中的數值作為操作數,這種定址方式是各類微處理器經常採用的一種方式,也是一種執行效率較高的定址方式。

寄存器定址是指操作數存放在CPU內部的寄存器中,指令中給出操作數所在的寄存器名。寄存器操作數可以是8位寄存器AH、AL、BH、BL、CH、CL、DH、DL,也可以是16位寄存器AX、BX、CX、DX、SP、BP、SI、DI等。因為寄存器定址不需要通過匯流排操作訪問存儲器,所以指令執行速度比較快。

寄存器定址( Register Addressing)是以通用寄存器的內容作為操作數的定址方式,在該定址方式下,操作數存放在寄存器中。寄存器定址方式的定址對象為:A,B,DPTR,RO~R7。其中,B僅在乘除法指令中為寄存器定址,在其他指令中為直接定址。A可以按寄存器定址又可以直接定址,直接定址時寫成ACC。

寄存器