半減法器

半減法器

在電腦的世界里,可以做任何數目系統而且複雜的演算,但是大多數的演算都藉由軟體(程式)來解決,而非用硬體(電路)直接進行各種演算,電腦的硬體或其他數位電路在做算術運算時,最基本的電路往往只有二進位加法器而已,至於減法可藉由補數的加法解決,乘法等於連續的加法,除法則是連續的減法,可見加法器在運算數位系統中的重要性,但它也不過是幾個邏輯閘就解決的電路,現在我們就先來瞭解二進加法的演算以及邏輯電路是如何做加法的。

減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構成,也可以由差分電路構成。基本集成運放電路有加、減、積分和微分等四種運算。一般是由集成運放外加反饋網路所構成的運算電路來實現。

信號處理電路的內容比較廣泛,包括有源濾波、精密二極體整流電路、電壓比較器和取樣-保持電路等。而這些信號處理電路都是由最基本的集成運放電路經過綜合設計而成的。因此對基本集成運放電路的熟悉和應運尤為重要。

減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構成,也可以由差分電路構成。

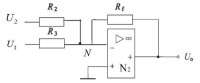

如果將兩個電壓相加,可以利用圖1所示電路來實現,這個電路接成反相放大器。

半減法器

利用虛短和虛斷的概念,N接點的接點方程為:

半減法器

半減法器

當 時,

半減法器

利用反相信號求和以實現減法運算

如圖2所示,第一級為反相比例放大電路

半減法器

半減法器

半減法器

若,則;第二級為反相加法電路,則可導出

半減法器

半減法器

若,則

半減法器

利用差分式電路以實現減法電路

圖3所示是用來實現兩個電壓相減的電路

半減法器

從電路結構上來看,它是反相輸入和同相輸入相結合的放大電路。在理想運放情況下,電路看成虛短現象,節點方程:

半減法器

半減法器

半減法器

其中,則

半減法器

半減法器

在上式中,如果滿足,輸出電壓可簡化為:

半減法器

在二進數目系統中只有兩個數字元號「0」與「1」,所以個位數的相加僅有以下四種可能:

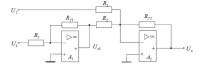

從表6.1-1中很快的可以看出和的輸出式S=A'B+AB',這不就是S=A⊕B嗎?而進位部份的輸出式CO=A.B,這個不含前級進位輸入的加法器如圖6.1-1所示,稱為半加器(Half-adder),它的電路僅需一個互斥或閘和一個及閘組合即可。

半加器僅解決了個位數相加的問題,如果多位元相加就得考慮前一位元相加之後的進位輸入Ci,就像圖6.1-2的方塊圖所示輸入端必須有一個Ci的接腳,這個電路的邏輯組合將是如何呢?其實只要依組合邏輯設計的步驟,很快的就知道答案了,但是為了證明全加器可以用兩個半加器及一個或閘組合而成,在以下的組合邏輯的設計過程中要特別留意化簡的方法。

步驟一

瞭解電路需求後,知道輸入端有3個,輸出端有2個。

步驟二

以真值表分析輸入及輸出之間的關係如表6.1-1。

步驟三

以卡諾圖化簡每一個輸出應有的項,並列出布林代數式。

步驟四

將布林代數式畫成電路圖。

步驟五

替換邏輯閘重繪電路,使得電路使用較少的IC。

將步驟四所得的電路框成以下的樣子,現在我們發現全加器(Full-Adder)可以用兩隻半加器及一個或閘來完成了。

步驟六

至此一個全加器已經完成,讀者可以在實驗室里依真值表的輸入條件測試其正確性,以加深印象。

有了全加器之後,一個長度為四位元的加法就可以用四個全加器加以完成如圖6.1-3所示,若加法中的位元增多時,僅需要將全加器並接至最高位元即可。