cc2430

cc2430

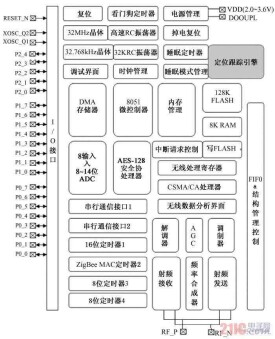

CC2430是一顆真正的系統晶元(SoC)CMOS解決方案。這種解決方案能夠提高性能並滿足以ZigBee為基礎的2.4GHz ISM波段應用,及對低成本,低功耗的要求。它結合一個高性能2.4GHz DSSS(直接序列擴頻)射頻收發器核心和一顆工業級小巧高效的8051控制器。 CC2430的設計結合了8Kbyte的RAM及強大的外圍模塊,並且有3種不同的版本,他們是根據不同的快閃記憶體空間32,64和128kByte來優化複雜度與成本的組合。

針對協議棧,網路和應用軟體的執行對MCU處理能力的要求,CC2430包含一個增強型工業標準的8位8051微控制器內核,運行時鐘32MHz。由於更快的執行時間和通過除去被浪費掉的匯流排狀態的方式,使得使用標準8051指令集的CC2430增強型8051內核,具有8倍的標準8051內核的性能。

CC2430集成了4個振蕩器用於系統時鐘和定時操作:一個32MHz晶體振蕩器,一個16MHz RC-振蕩器,一個可選的32.768kHz晶體振蕩器和一個可選的32.768kHz RC 振蕩器。

CC2430也集成了用於用戶自定義應用的外設。一個AES協處理器被集成在CC2430,以支持IEEE802.15.4 MAC 安全所需的(128位關鍵字)AES的運行,以實現儘可能少的佔用微控制器。

中斷控制器為總共18個中斷源提供服務,他們中的每個中斷都被賦予4個中斷優先順序中的某一個。調試介面採用兩線串列介面,該介面被用於在電路調試和外部Flash編程。I/O控制器的職責是21個一般I/O口的靈活分配和可靠控制。

CC2430包括四個定時器:一個16位MAC定時器,用以為IEEE802.15.4的CSMA-CA演演算法提供定時以及為IEEE802.15.4的MAC層提供定時。一個一般的16位和兩個8位定時器,支持典型的定時/計數功能,例如,輸入捕捉、比較輸出和PWM功能。

CC2430內集成的其他外設有:

為了更好的處理網路和應用操作的帶寬,CC2430集成了大多數對定時要求嚴格的一系列IEEE802.15.4 MAC協議,以減輕微控制器的負擔。這包括:

* 自動前導幀發生器

*同步字插入/檢測

* CRC-16校驗

* CCA

* 信號強度檢測/數字RSSI

* 連接品質指示(LQI)

*CSMA/CA協處理器

CC2430的接收器是基於低-中頻結構之上的,從天線接收的RF信號經低雜訊放大器放大並經下變頻變為2MHz的中頻信號。中頻信號經濾波、放大,在通過A/D轉換器變為數字信號。自動增益控制,通道過濾,解調在數字域完成以獲得高精確度及空間利用率。集成的模擬通道濾波器可以使工作在2.4GHz ISM波段的不同系統良好的共存。

在發射模式下,位映射和調製是根據IEEE 802.15.4的規範來完成的。調製(和擴頻)通過數字方式完成。被調製的基帶信號經過D/A轉換器再由單邊帶調製器進行低通濾波和直接上變頻變為射頻信號。最終,高頻信號經過片內功率放大器放大以達到可設計的水平。

射頻的輸入輸出埠是獨立的,他們分享兩個普通的PIN引腳。CC2430不需要外部TX/RX開關,其開關已集成在晶元內部。晶元至天線之間電路的構架是由平衡/非平衡器與少量低價電容與電感所組成。可替代的,一個平衡式天線,如對摺式偶極天線也是可以實現上述功能的。集成在內部的頻率合成器可去除對環路濾波器和外部被動式壓控振蕩器的需要。晶片內置的偏壓可變電容壓控振蕩器工作在一倍本地振蕩頻率範圍,另搭配了二分頻電路,以提供四相本地振蕩信號給上、下變頻綜合混頻器使用。

CC2430 晶元延用了以往CC2420 晶元的架構,在單個晶元上整合了ZigBee 射頻(RF)

前端、內存和微控制器。它使用1 個8 位MCU(8051),具有128 KB 可編程快閃記憶體和8 KB

狗定時器(Watchdog timer)、32 kHz 晶振的休眠模式定時器、上電複位電路(Power On

Reset)、掉電檢測電路(Brown out detection),以及21 個可編程I/O 引腳。

CC2430 晶元採用0.18 μm CMOS 工藝生產;在接收和發射模式下,電流損耗分別低

於27 mA 或25 mA。CC2430 的休眠模式和轉換到主動模式的超短時間的特性,特別適合那

些要求電池壽命非常長的應用。

◆ 高性能和低功耗的8051 微控制器核。

◆ 集成符合IEEE802.15.4 標準的2.4 GHz 的 RF 無線電收發機。

◆ 優良的無線接收靈敏度和強大的抗干擾性。

◆ 在休眠模式時僅0.9 μA 的流耗,外部的中斷或RTC 能喚醒系統;在待機模式時少

於0.6 μA 的流耗,外部的中斷能喚醒系統。

◆ 硬體支持CSMA/CA 功能。

◆ 較寬的電壓範圍(2.0~3.6 V)。

◆ 數字化的RSSI/LQI 支持和強大的DMA 功能。

◆ 具有電池監測和溫度感測功能。

◆ 集成了14 位模數轉換的ADC。

◆ 集成 AES 安全協處理器。

◆ 帶有 2 個強大的支持幾組協議的USART,以及1 個符合IEEE 802.15.4 規範的MAC

計時器,1 個常規的16 位計時器和2 個8 位計時器。

◆ 強大和靈活的開發工具。

CC2430 晶元採用7 mm×7mm QLP封裝,共有48 個引腳。全部引腳可分為I/O 埠線

引腳、電源線引腳和控制線引腳三類。

CC2430 有21 個可編程的I/O 口引腳,P0、P1 口是完全的8 位口,P2 口只有5 個可使

用的位。通過軟體設定一組SFR 寄存器的位和位元組,可使這些引腳作為通常的I/O 口或作

為連接ADC、計時器或USART 部件的外圍設備I/O 口使用。

I/O 口有下面的關鍵特性:

◆ 可設置為通常的I/O 口,也可設置為外圍I/O 口使用。

◆ 在輸入時有上拉和下拉能力。

◆ 全部 21 個數字I/O 口引腳都具有響應外部的中斷能力。如果需要外部設備,可對I/O

口引腳產生中斷,同時外部的中斷事件也能被用來喚醒休眠模式。

1~6 腳(P1_2~ P1_7):具有 4 mA 輸出驅動能力。

8,9 腳(P1_0,P1_1):具有 20 mA 的驅動能力。

11~18 腳(P0_0 ~P0_7):具有 4 mA 輸出驅動能力。

43,44,45,46,48 腳(P2_4,P2_3,P2_2,P2_1,P2_0):具有4 mA 輸出驅動能力。

7 腳(DVDD):為 I/O 提供2.0~3.6 V 工作電壓。

20 腳(AVDD_SOC):為模擬電路連接2.0~3.6 V 的電壓。

23 腳(AVDD_RREG):為模擬電路連接2.0~3.6 V 的電壓。

24 腳(RREG_OUT):為 25,27~31,35~40引腳埠提供1.8 V 的穩定電壓。

25 腳 (AVDD_IF1 ):為接收器波段濾波器、模擬測試模塊和VGA 的第一部分電路提

供1.8 V 電壓。

27 腳(AVDD_CHP):為環狀濾波器的第一部分電路和充電泵提供1.8 V 電壓。

28 腳(VCO_GUARD): VCO 屏蔽電路的報警連接埠。

29 腳(AVDD_VCO): 為VCO 和PLL 環濾波器最後部分電路提供1.8 V 電壓。

30 腳(AVDD_PRE): 為預定標器、Div 2 和LO 緩衝器提供1.8 V 的電壓。

31 腳(AVDD_RF1): 為LNA、前置偏置電路和PA 提供1.8 V 的電壓。

33 腳(TXRX_SWITCH): 為PA 提供調整電壓。

35 腳(AVDD_SW): 為LNA/PA 交換電路提供1.8 V 電壓。

36 腳(AVDD_RF2): 為接收和發射混頻器提供1.8 V 電壓。

37 腳(AVDD_IF2): 為低通濾波器和VGA 的最後部分電路提供1.8 V 電壓。

38 腳(AVDD_ADC): 為ADC 和DAC 的模擬電路部分提供1.8 V 電壓。

39 腳(DVDD_ADC): 為ADC 的數字電路部分提供1.8 V 電壓。

40 腳(AVDD_DGUARD): 為隔離數字雜訊電路連接電壓。

41 腳(AVDD_DREG): 向電壓調節器核心提供2.0~3.6 V 電壓。

42 腳(DCOUPL): 提供1.8 V 的去耦電壓,此電壓不為外電路所使用。

47 腳(DVDD): 為I/O 埠提供2.0~3.6 V 的電壓。

2.3 控制線引腳功能

10 腳(RESET_N): 複位引腳,低電平有效。

19 腳(XOSC_Q2): 32 MHz 的晶振引腳2。

21 腳(XOSC_Q1): 32 MHz 的晶振引腳1,或外部時鐘輸入引腳。

22 腳(RBIAS1): 為參考電流提供精確的偏置電阻。

26 腳(RBIAS2): 提供精確電阻,43 kΩ,±1%。

32 腳(RF_P): 在RX 期間向LNA 輸入正向射頻信號;在TX 期間接收來自PA 的輸

入正向射頻信號。

34 腳(RF_N): 在RX 期間向LNA 輸入負向射頻信號;在TX 期間接收來自PA 的輸

入負向射頻信號。

43 腳 (P2_4/XOSC_Q2): 32.768 kHz XOSC 的2.3 埠。

44 腳 (P2_4/XOSC_Q1): 32.768 kHz XOSC 的2.4 埠。