邏輯電路

以二進位為原理的電路

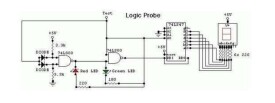

邏輯電路是一種離散信號的傳遞和處理,以二進位為原理、實現數字信號邏輯運算和操作的電路。分組合邏輯電路和時序邏輯電路。前者由最基本的“與門”電路、“或門電路”和“非門”電路組成,其輸出值僅依賴於其輸入變數的當前值,與輸入變數的過去值無關——即不具記憶和存儲功能;後者也由上述基本邏輯門電路組成,但存在反饋迴路——它的輸出值不僅依賴於輸入變數的當前值,也依賴於輸入變數的過去值。由於只分高、低電平,抗干擾力強,精度和保密性佳。廣泛應用於計算機、數字控制、通信、自動化和儀錶等方面。最基本的有與電路、或電路和非電路。

簡單的邏輯電路通常是由門電路構成,也可以用三極體來製作,例如,一個NPN三極體的集電極和另一個NPN三極體的發射極連接,這就可以看作是一個簡單的與門電路,即:當兩個三極體的基極都接高電平的時候,電路導通,而只要有一個不接高電平,電路就不導通。

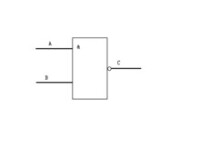

常見的門電路如下所示:

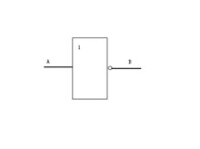

邏輯電路

| A | B |

| 1 | |

| 1 |

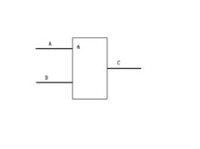

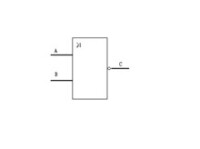

邏輯電路

| A | B | C |

| 1 | ||

| 1 | ||

| 1 | 1 | 1 |

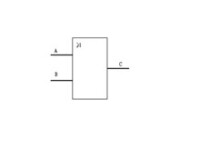

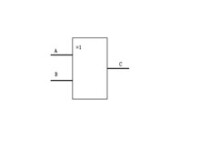

邏輯電路

| A | B | C |

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 | 1 |

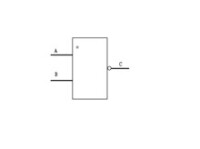

邏輯電路

| A | B | C |

| 1 | ||

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 |

邏輯電路

| A | B | C |

| 1 | ||

| 1 | ||

| 1 | ||

| 1 | 1 |

邏輯電路

| A | B | C |

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 |

邏輯電路

| A | B | C |

| 1 | ||

| 1 | ||

| 1 | ||

| 1 | 1 | 1 |

在asic設計和pld設計中組合邏輯電路設計的最簡化是很重要的,在設計時常要求用最少的邏輯門或導線實現。在asic設計和pld設計中需要處理大量的約束項,值為1或0的項卻是有限的,提出組合邏輯電路設計的一種新方法。與邏輯表示只有在決定事物結果的全部條件具備時,結果才發生的因果關係。輸出變數為1的某個組合的所有因子的與表示輸出變數為1的這個組合出現、所有輸出變數為0的組合均不出現,因而可以表示輸出變數為1的這個組合。

組合邏輯電路的分析分以下幾個步驟:

(1)有給定的邏輯電路圖,寫出輸出端的邏輯表達式;

(2)列出真值表;

(3)通過真值表概括出邏輯功能,看原電路是不是最理想,若不是,則對其進行改進。