去耦電容

去耦電容

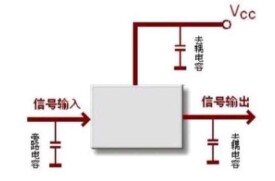

在共享導體的電路中,共享電源的時候,當一個器件需要對外提供輸出的時候就會同時拉低該導體的電壓,產生雜訊耦合到共享的電路中。在有雜訊的環境中,這些電磁波會在導體內感應出電壓信號,影響迴路中的元件。在數位電路中,器件容易在臨界位置由於干擾而產生錯誤的信號,從而產生錯誤的動作。去耦電容可以減少以上情形的發生。

去耦電容一般都安置在元件附近的電源處,以減少布線阻抗對濾波效果的影響。去耦電容多使用瓷片電容,其數值由電壓信號最快上升和下降速度確定。

去耦電容

去耦電容就是起到一個電池的作用,滿足驅動電路電流的變化,避免相互間的耦合干擾。

去耦和旁路都可以看作濾波。去耦電容相當於電池,避免由於電流的突變而使電壓下降,相當於濾紋波。具體容值可以根據電流的大小、期望的紋波大小、作用時間的大小來計算。去耦電容一般都很大,對更高頻率的雜訊,基本無效。旁路電容就是針對高頻來的,也就是利用了電容的頻率阻抗特性。電容一般都可以看成一個RLC串聯模型。在某個頻率,會發生諧振,此時電容的阻抗就等於其ESR。如果看電容的頻率阻抗曲線圖,就會發現一般都是一個V形的曲線。具體曲線與電容的介質有關,所以選擇旁路電容還要考慮電容的介質,一個比較保險的方法就是多並幾個電容。

去耦電容主要是去除高頻如RF信號的干擾,干擾的進入方式是通過電磁輻射。

而實際上,晶元附近的電容還有蓄能的作用,這是第二位的。你可以把總電源看作密雲水庫,我們大樓內的家家戶戶都需要供水,這時候,水不是直接來自於水庫,那樣距離太遠了,等水過來,我們已經渴的不行了。實際水是來自於大樓頂上的水塔,水塔其實是一個緩衝器的作用。如果微觀來看,高頻器件在工作的時候,其電流是不連續的,而且頻率很高,而器件VCC到總電源有一段距離,即便距離不長,在頻率很高的情況下,阻抗Z=i*wL+R,線路的電感影響也會非常大,會導致器件在需要電流的時候,不能被及時供給。而去耦電容可以彌補此不足。這也是為什麼很多電路板在高頻器件VCC管腳處放置小電容的原因之一。

有源器件在開關時產生的高頻開關雜訊將沿著電源線傳播。去耦電容的主要功能就是提供一個局部的直流電源給有源器件,以減少開關雜訊在板上的傳播和將雜訊引導到地。

去耦電容