8253晶元

8253晶元

8253晶元是可編程計數器/定時器。這種晶元外形引腳都是兼容性的。8253內部有三個計數器,分別稱為計數器0、計數器1和計數器2,他們的機構完全相同。

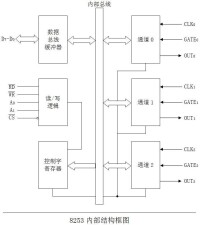

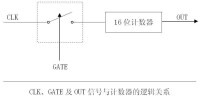

每個計數器的輸入和輸出都決定於設置在控制寄存器中的控制字,互相之間工作完全獨立。每個計數器通過三個引腳和外部聯繫,一個為時鐘輸入端CLK,一個為門控信號輸入端GATE,另一個為輸出端OUT。每個計數器內部有一個8位的控制寄存器,還有一個16位的計數初值寄存器CR、一個計數執行部件CE和一個輸出鎖存器OL。

intel8253是NMOS工藝製成的可編程計數器/定時器,有幾種晶元型號,外形引腳及功能都是兼容的,只是工作的最高計數速率有所差異,例如8253(2.6MHz),8253-5(5MHz)

8253內部結構框圖

8253晶元

執行部件實際上是一個16位的減法計數器,它的起始值就是初值寄存器的值,而初始值寄存器的值是通過程序設置的。輸出鎖存器的值是通過程序設置的。輸出鎖存器OL用來鎖存計數執行部件CE的內容,從而使CPU可以對此進行讀操作。順便提一下,CR、CE和OL都是16位寄存器,但是也可以作8位寄存器來用。

8253具有3個獨立的計數通道,採用減1計數方式。在門控信號有效時,每輸入1個計數脈衝,通道作1次計數操作。當計數脈衝是已知周期的時鐘信號時,計數就成為定時。

一、8253內部結構

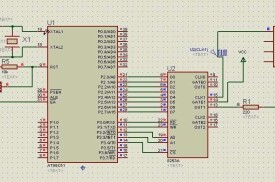

8253晶元有24條引腳,封裝在雙列直插式陶瓷管殼內。

1.數據匯流排緩衝器

數據匯流排緩衝器與系統匯流排連接,8位雙向,與CPU交換信息的通道。這是8253與CPU之間的數據介面,它由8位雙向三態緩衝存儲器構成,是CPU與8253之間交換信息的必經之路。

8253晶元

讀/寫控制分別連接系統的IOR#和IOW#,由CPU控制著訪問8253的內部通道。接收CPU送入的讀/寫控制信號,並完成對晶元內部各功能部件的控制功能,因此,它實際上是8253晶元內部的控制器。A1A0:埠選擇信號,由CPU輸入。8253內部有3個獨立的通道,加上控制字寄存器,構成8253晶元的4個埠,CPU可對3個通道進行讀/寫操作3對控制字寄存器進行寫操作。這4個埠地址由最低2位地址碼A1和A0來選擇。如表所示。

3.通道選擇

(1)CS#——片選信號,由CPU輸入,低電平有效,通常由埠地址的高位地址解碼形成。

(2)RD#、WR#——讀/寫控制命令,由CPU輸入,低電平有效。RD#效時,CPU讀取由A1A0所選定的通道內計數器的內容。WR#有效時,CPU將計數值寫入各個通道的計數器中,或者是將方式控制字寫入控制字寄存器中。CPU對8253的讀/寫操作。

4.計數通道0~2

每個計數通道內含1個16位的初值寄存器、減1計數器和1個16位的(輸出)鎖存器。8253內部包含3個功能完全相同的通道,每個通道內部設有一個16位計數器,可進行二進位或十進位(BCD碼)計數。採用二進位計數時,寫入的初值範圍為0000H~0FFFFH,最大計數值是0000H,代表65536。採用BCD碼計數時,寫入的初值範圍為0000~9999,最大計數值是0000,代表10000。與此計數器相對應,每個通道內設有一個16位計數值鎖存器。必要時可用來鎖存計數值。(特別說明:8253計數器的值先減1再判斷是否為0,為0就中斷了,所以最大初始值為0,這樣減1以後,不為0,所以為最大的,取決於CF標誌位)

當某通道用作計數器時,應將要求計數的次數預置到該通道的計數器中、被計數的事件應以脈衝方式從CLK端輸入,每輸入一個計數脈衝,計數器內容減“1”,待計數值計到“0”。OUT端將有輸出。表示計數次數到。當某個通道用作定時器時。由CLK輸入一定頻率的時鐘脈衝。根據要求定時的時間長短確定所需的計數值。並預置到計數器中,每輸入一個時鐘脈衝,計數器內容減“1”,待計數值計到“0”。OUT將有輸出,表示定時時間到。允許從CLK輸入的時鐘頻在1~2MHz範圍內。因此,任一通道作計數器用或作定時器用,其內部操作完全相同,區別僅在於前者是由計數脈衝進行減“1”計數。而後者是內時鐘脈衝進行減“1”計數。作計數器時,要求計數的次數可直接作為計數器的初值預置到減“1”計數器中。作定時器時,計數器的初值即定時係數應根據要求定時的時間進行如下運算才能得到:

定時係數=需要定時的時間/時鐘脈衝周期

①設置通道:向方式控制字寄存器埠寫入方式選擇控制字,用於確定要設置的通道及工作方式;

②計數/定時:向通道寫入計數值,啟動計數操作;

③讀取當前的計數值:向指定通道讀取當前計數器值時,8253將計數器值存入鎖存器,從鎖存器向外提供當前的計數器值,計數器則繼續作計數操作。

④計數到:當計數器減1為0時,通過引腳OUTi向外輸出“到”的脈衝信號。

計數初值輸入存放在初值寄存器中,計數開始或重裝入時被複制到計數器中。

8253晶元

5.方式選擇控制字

8253的初始化編程就是對其工作方式的確定。具體實現就是在8253上電后,由CPU向8253的控制寄存器寫入一個控制字,就可以規定8253的工作方式、計數值的長度以及計數所用的數制等,另外根據要求將計數值寫入8253的相應通道。

8253的一個方式控制字只決定一個技術通道的工作模式。

二、8253的通道工作方式

8253中各通道可有6種可供選擇的工作方式,以完成定時、計數或脈衝發生器等多種功能。8253的各種工作方式如下:

1.方式0:計數結束則中斷

工作方式0被稱為計數結束中斷方式。當任一通道被定義為工作方式0時,OUTi輸出為低電平;若門控信號GATE為高電平,當CPU利用輸出指令向該通道寫入計數值WR#有效時,OUTi仍保持低電平,然後計數器開始減“1”計數,直到計數值為“0”,此刻OUTi將輸出由低電平向高電平跳變,可用它向CPU發出中斷請求,OUTi端輸出的高電平一直維持到下次再寫入計數值為止。

在工作方式0情況下,門控信號GATE用來控制減“1”計數操作是否進行。當GATE=1時,允許減“1”計數;GATE=0時,禁止減“1”計數;計數值將保持GATE有效時的數值不變,待GATE重新有效后,減“1”計數繼續進行。

顯然,利用工作方式0既可完成計數功能,也可完成定時功能。當用作計數器時,應將要求計數的次數預置到計數器中,將要求計數的事件以脈衝方式從CLKi端輸入,由它對計數器進行減“1”計數,直到計數值為0,此刻OUTi輸出正跳變,表示計數次數到。當用作定時器時,應把根據要求定時的時間和CLKi的周期計算出定時係數,預置到計數器中。從CLKi,輸入的應是一定頻率的時鐘脈衝,由它對計數器進行減“1”計數,定時時間從寫入計數值開始,到計數值計到“0”為止,這時OUTi輸出正跳變,表示定時時間到。

有一點需要說明,任一通道工作在方式0情況下,計數器初值一次有效,經過一次計數或定時后如果需要繼續完成計數或定時功能,必須重新寫入計數器的初值。

2.方式1:單脈衝發生器

工作方式1被稱作可編程單脈衝發生器。進入這種工作方式,CPU裝入計數值n后OUTi輸出高電平,不管此時的GATE輸入是高電平還是低電平,都不開始減“1”計數,必須等到GATE由低電平向高電平跳變形成一個上升沿后,計數過程才會開始。與此同時,OUTi輸出由高電平向低電平跳變,形成了輸出單脈衝的前沿,待計數值計到“0”,OUTi輸出由低電平向高電平跳變,形成輸出單脈衝的后沿,因此,由方式l所能輸出單脈衝的寬度為CLKi周期的n倍。

如果在減“1”計數過程中,GATE由高電平跳變為低電乎,這並不影響計數過程,仍繼續計數;但若重新遇到GATE的上升沿,則從初值開始重新計數,其效果會使輸出的單脈衝加寬,如教材圖9-22(b)中的第2個單脈衝。

這種工作方式下,計數值也是一次有效,每輸入一次計數值,只產生一個負極性單脈衝。

3.方式2:速率波發生器

工作方式2被稱作速率波發生器。進入這種工作方式,OUTi輸出高電平,裝入計數值n后如果GATE為高電平,則立即開始計數,OUTi保持為高電平不變;待計數值減到“1”和“0”之間,OUTi將輸出寬度為一個CLKi周期的負脈衝,計數值為“0”時,自動重新裝入計數初值n,實現循環計數,OUTi將輸出一定頻率的負脈衝序列,其脈衝寬度固定為一個CLKi周期,重複周期為CLKi周期的n倍。

如果在減“1”計數過程中,GATE變為無效(輸入0電平),則暫停減“1”計數,待GATE恢復有效后,從初值n開始重新計數。這樣會改變輸出脈衝的速率。

如果在操作過程中要求改變輸出脈衝的速率,CPU可在任何時候,重新寫入新的計數值,它不會影響正在進行的減“1”計數過程,而是從下一個計數操作用期開始按新的計數值改變輸出脈衝的速率。

4.方式3:方波發生器

工作方式3被稱作方波發生器。任一通道工作在方式3,只在計數值n為偶數,則可輸出重複周期為n、占空比為1:1的方波。

進入工作方式3,OUTi輸出低電平,裝入計數值后,OUTi立即跳變為高電平。如果當GATE為高電平,則立即開始減“1”計數,OUTi保持為高電平,若n為偶數,則當計數值減到n/2時,OUTi跳變為低電平,一直保持到計數值為“0”,系統才自動重新置入計數值n,實現循環計數。這時OUTi端輸出的周期為n×CLKi周期,占空比為1:1的方波序列;若n為奇數,則OUTi端輸出周期為n×CLKi周期,占空比為((n+1)/2)/((n-1)/2)的近似方波序列。

如果在操作過程中,GATE變為無效,則暫停減“1”計數過程,直到GATE再次有效,重新從初值n開始減“l”計數。

如果要求改變輸出方波的速率,則CPU可在任何時候重新裝入新的計數初值n,並從下一個計數操作周期開始改變輸出方波的速率。

5.方式4:軟體觸發方式計數

工作方式4被稱作軟體觸發方式。進入工作方式4,OUTi輸出高電平。裝入計數值n后,如果GATE為高電平,則立即開始減“1”計數,直到計數值減到“0”為止,OUTi輸出寬度為一個CLKi周期的負脈衝。由軟體裝入的計數值只有一次有效,如果要繼續操作,必須重新置入計數初值n。如果在操作的過程中,GATE變為無效,則停止減“1”計數,到GATE再次有效時,重新從初值開始減“1”計數。

顯然,利用這種工作方式可以完成定時功能,定時時間從裝入計數值n開始,則OUTi輸出負脈衝(表示定時時間到),其定時時間=n×CLK周期。這種工作方式也可完成計數功能,它要求計數的事件以脈衝的方式從CLKi輸入,將計數次數作為計數初值裝入后,由CLKi端輸入的計數脈衝進行減“1”計數,直到計數值為“0”,由OUTt端輸出負脈衝(表示計數次數到)。當然也可利用OUTj向CFU發出中斷請求。因此工作方式4與工作方式0很相似,只是方式0在OUTi端輸出正階躍信號、方式4在OUTi端輸出負脈衝信號。

6.方式5:硬體觸發方式計數

工作方式5被稱為硬體觸發方式。進入工作方式5,OUTi輸出高電平,硬體觸發信號由GATE端引入。因此,開始時GATE應輸入為0,裝入計數初值n后,減“1”計數並不工作,一定要等到硬體觸發信號由GATE端引入一個正階躍信號,減“1”計數才會開始,待計數值計到“0”,OUTi將輸出負脈衝,其寬度固定為一個CLKi周期,表示定時時間到或計數次數到。

這種工作方式下,當計數值計到“0”后,系統將自動重新裝入計數值n,但並不開始計數,一定要等到由GATE端引入的正跳沿,才會開始進行減“1”計數,因此這是一種完全由GATE端引入的觸發信號控制下的計數或定時功能。如果由CLKi輸入的是一定頻率的時鐘脈衝,那麼可完成定時功能,定時時間從GATE上升沿開始,到OUTi端輸出負脈衝結束。如果從CLKi端輸入的是要求計數的事件,則可完成計數功能,計數過程從GATE上升沿開始,到OUTi輸出負脈衝結束。GATE可由外部電路或控制現場產生,故硬體觸發方式由此而得名。

如果需要改變計數初值,CPU可在任何時候用輸出指令裝入新的計數初值m,它將不影響正在進行的操作過程,而是到下一個計數操作周期才會按新的計數值進行操作。

從上述各工作方式可看出,GATE作為各通道的門控信號,對於各種不同的工作方式,它所起的作用各不相同。在8253的應用中,必須正確使用GATE信號,才能保證各通道的正常操作。

7.讀取計數器的當前值

⑴直接讀計數器:輸出鎖存器在非鎖存狀態會跟隨計數器計數的變化而變化,直接讀計數器是從鎖存器得到計數器的當前值。但由於計數器處於工作狀態,讀出值不一定能穩定。

⑵先鎖存再讀取:①通過方式選擇控制字對指定通道(SC1、SC0)的計數值鎖入鎖存器(RL1RL0=00),鎖存器一旦鎖存了當前計數值,就不再隨計數器變化直到被讀取。②讀計數器通道(有鎖存器)。