控制寄存器

控制寄存器

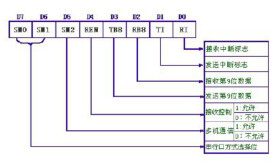

控制寄存器(CR0~CR3)用於控制和確定處理器的操作模式以及當前執行任務的特性,如圖4-3所示。CR0中含有控制處理器操作模式和狀態的系統控制標誌;CR1保留不用;CR2含有導致頁錯誤的線性地址;CR3中含有頁目錄表物理內存基地址,因此該寄存器也被稱為頁目錄基地址寄存器PDBR(Page-Directory Base address Register)。

目錄

控制寄存器

控制寄存器

1.CR0中協處理器控制位

CR0的4個位:擴展類型位ET、任務切換位TS、模擬位EM和數學存在位MP用於控制80x86浮點(數學)協處理器的操作。有關協處理器的詳細說明請參見第11章內容。CR0的ET位(標誌)用於選擇與協處理器進行通信所使用的協議,即指明系統中使用的是80387還是80287協處理器。TS、MP和EM位用於確定浮點指令或WAIT指令是否應該產生一個設備不存在(Device Not Available,DNA)異常。這個異常可用來僅為使用浮點運算的任務保存和恢復浮點寄存器。對於沒有使用浮點運算的任務,這樣做可以加快它們之間的切換操作。

(1)ET:CR0的位4是擴展類型(Extension Type)標誌。當該標誌為1時,表示指明系統中有80387協處理器,並使用32位協處理器協議。ET=0指明使用80287協處理器。如果模擬位EM=1,則該位將被忽略。在處理器複位操作時,ET位會被初始化指明系統中使用的協處理器類型。如果系統中有80387,則ET被設置成1,否則若有一個80287或者沒有協處理器,則ET被設置成0。

(2)TS:CR0的位3是任務已切換(Task Switched)標誌。該標誌用於推遲保存任務切換時的協處理器內容,直到新任務開始實際執行協處理器指令。處理器在每次任務切換時都會設置該標誌,並且在執行協處理器指令時測試該標誌。

如果設置了TS標誌並且CR0的EM標誌為0,那麼在執行任何協處理器指令之前會產生一個設備不存在異常。如果設置了TS標誌但沒有設置CR0的MP和EM標誌,那麼在執行協處理器指令WAIT/FWAIT之前不會產生設備不存在異常。如果設置了EM標誌,那麼TS標誌對協處理器指令的執行無影響,見表4-1。

表4-1 CR0中標誌EM、MP和TS的不同組合對協處理器指令動作的影響

| CR0中的標誌 | 指令類型 | |||

| EM | MP | TS | 浮點 | WAIT/FWAIT |

| 執行 | 執行 | |||

| 1 | 設備不存在(DNA)異常 | 執行 | ||

| 1 | 執行 | 執行 | ||

| 1 | 1 | DNA異常 | DNA異常 | |

| 1 | DNA異常 | 執行 | ||

| 1 | 1 | DNA異常 | 執行 | |

| 1 | 1 | DNA異常 | 執行 | |

| 1 | 1 | 1 | DNA異常 | DNA異常 |

在任務切換時,處理器並不自動保存協處理器的上下文,而是會設置TS標誌。這個標誌會使得處理器在執行新任務指令流的任何時候遇到一條協處理器指令時產生設備不存在異常。設備不存在異常的處理程序可使用CLTS指令清除TS標誌,並且保存協處理器的上下文。如果任務從沒有使用過協處理器,那麼相應協處理器上下文就不用保存。

(3)EM:CR0的位2是模擬(EMulation)標誌。當該位設置時,表示處理器沒有內部或外部協處理器,執行協處理器指令時會引起設備不存在異常;當清除時,表示系統有協處理器。設置這個標誌可以迫使所有浮點指令使用軟體來模擬。

(4)MP:CR0的位1是監控協處理器(Monitor coProcessor或Math Present)標誌。用於控制WAIT/FWAIT指令與TS標誌的交互作用。如果MP=1、TS=1,那麼執行WAIT指令將產生一個設備不存在異常;如果MP=0,則TS標誌不會影響WAIT的執行。

2.CR0中保護控制位

(1)PE:CR0的位0是啟用保護(Protection Enable)標誌。當設置該位時即開啟了保護模式;當複位時即進入實地址模式。這個標誌僅開啟段級保護,而並沒有啟用分頁機制。若要啟用分頁機制,那麼PE和PG標誌都要置位。

(2)PG:CR0的位31是分頁(Paging)標誌。當設置該位時即開啟了分頁機制;當複位時則禁止分頁機制,此時所有線性地址等同於物理地址。在開啟這個標誌之前必須已經或者同時開啟PE標誌。即若要啟用分頁機制,那麼PE和PG標誌都要置位。

(3)WP:對於Intel 80486或以上的CPU,CR0的位16是防寫(Write Proctect)標誌。當設置該標誌時,處理器會禁止超級用戶程序(例如特權級0的程序)向用戶級只讀頁面執行寫操作;當該位複位時則反之。該標誌有利於UNIX類操作系統在創建進程時實現寫時複製(Copy on Write)技術。

(4)NE:對於Intel 80486或以上的CPU,CR0的位5是協處理器錯誤(Numeric Error)標誌。當設置該標誌時,就啟用了x87協處理器錯誤的內部報告機制;若複位該標誌,那麼就使用PC形式的x87協處理器錯誤報告機制。當NE為複位狀態並且CPU的IGNNE輸入引腳有信號時,那麼數學協處理器x87錯誤將被忽略。當NE為複位狀態並且CPU的IGNNE輸入引腳無信號時,那麼非屏蔽的數學協處理器x87錯誤將導致處理器通過FERR引腳在外部產生一個中斷,並且在執行下一個等待形式浮點指令或WAIT/FWAIT指令之前立刻停止指令執行。CPU的FERR引腳用於模擬外部協處理器80387的ERROR引腳,因此通常連接到中斷控制器輸入請求引腳上。NE標誌、IGNNE引腳和FERR引腳用於利用外部邏輯來實現PC形式的外部錯誤報告機制。

啟用保護模式PE(Protected Enable)位(位0)和開啟分頁PG(Paging)位(位31)分別用於控制分段和分頁機制。PE用於控制分段機制。如果PE=1,處理器就工作在開啟分段機制環境下,即運行在保護模式下。如果PE=0,則處理器關閉了分段機制,並如同8086工作於實地址模式下。PG用於控制分頁機制。如果PG=1,則開啟了分頁機制。如果PG=0,分頁機制被禁止,此時線性地址被直接作為物理地址使用。

如果PE=0、PG=0,處理器工作在實地址模式下;如果PG=0、PE=1,處理器工作在沒有開啟分頁機制的保護模式下;如果PG=1、PE=0,此時由於不在保護模式下不能啟用分頁機制,因此處理器會產生一個一般保護異常,即這種標誌組合無效;如果PG=1、PE=1,則處理器工作在開啟了分頁機制的保護模式下。

當改變PE和PG位時,必須小心。只有當執行程序至少有部分代碼和數據在線性地址空間和物理地址空間中具有相同地址時,我們才能改變PG位的設置。此時這部分具有相同地址的代碼在分頁和未分頁世界之間起著橋樑的作用。無論是否開啟分頁機制,這部分代碼都具有相同的地址。另外,在開啟分頁(PG=1)之前必須先刷新頁高速緩衝TLB。

在修改該了PE位之後程序必須立刻使用一條跳轉指令,以刷新處理器執行管道中已經獲取的不同模式下的任何指令。在設置PE位之前,程序必須初始化幾個系統段和控制寄存器。在系統剛上電時,處理器被複位成PE=0和PG=0(即實模式狀態),以允許引導代碼在啟用分段和分頁機制之前能夠初始化這些寄存器和數據結構。

3.CR2和CR3

CR2和CR3用於分頁機制。CR3含有存放頁目錄表頁面的物理地址,因此CR3也被稱為PDBR。因為頁目錄表頁面是頁對齊的,所以該寄存器只有高20位是有效的。而低12位保留供更高級處理器使用,因此在往CR3中載入一個新值時低12位必須設置為0。

使用MOV指令載入CR3時具有讓頁高速緩衝無效的副作用。為了減少地址轉換所要求的匯流排周期數量,最近訪問的頁目錄和頁表會被存放在處理器的頁高速緩衝器件中,該緩衝器件被稱為轉換查找緩衝區(Translation Lookaside Buffer,TLB)。只有當TLB中不包含要求的頁表項時才會使用額外的匯流排周期從內存中讀取頁表項。

即使CR0中的PG位處於複位狀態(PG=0),我們也能先載入CR3。以允許對分頁機制進行初始化。當切換任務時,CR3的內容也會隨之改變。但是如果新任務的CR3值與原任務的一樣,處理器就無需刷新頁高速緩衝。這樣共享頁表的任務可以執行得更快。

CR2用於出現頁異常時報告出錯信息。在報告頁異常時,處理器會把引起異常的線性地址存放在CR2中。因此操作系統中的頁異常處理程序可以通過檢查CR2的內容來確定線性地址空間中哪一個頁面引發了異常。