I2C匯流排

Philips公司開發的匯流排

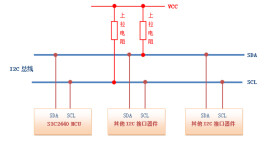

I2C匯流排是由Philips公司開發的一種簡單、雙向二線制同步串列匯流排。它只需要兩根線即可在連接於匯流排上的器件之間傳送信息。

SDA(串列數據線)和SCL(串列時鐘線)都是雙向I/O線,介面電路為開漏輸出.需通過上拉電阻接電源VCC.當匯流排空閑時.兩根線都是高電平,連接匯流排的外同器件都是CMOS器件,輸出級也是開漏電路.在匯流排上消耗的電流很小,因此,匯流排上擴展的器件數量主要由電容負載來決定,因為每個器件的匯流排介面都有一定的等效電容.而線路中電容會影響匯流排傳輸速度.當電容過大時,有可能造成傳輸錯誤.所以,其負載能力為400pF,因此可以估算出匯流排允許長度和所接器件數量。

主器件用於啟動匯流排傳送數據,併產生時鐘以開放傳送的器件,此時任何被定址的器件均被認為是從器件.在匯流排上主和從、發和收的關係不是恆定的,而取決於此時數據傳送方向。如果主機要發送數據給從器件,則主機首先定址從器件,然後主動發送數據至從器件,最後由主機終止數據傳送;如果主機要接收從器件的數據,首先由主器件定址從器件.然後主機接收從器件發送的數據,最後由主機終止接收過程。在這種情況下.主機負責產生定時時鐘和終止數據傳送。

I2C匯流排特點可以概括如下:

(1)在硬體上,12C匯流排只需要一根數據線和一根時鐘線兩根線,匯流排介面已經集成在晶元內部,不需要特殊的介面電路,而且片上介面電路的濾波器可以濾去匯流排數據上的毛刺.因此I2C匯流排簡化了硬體電路PCB布線,降低了系統成本,提高了系統可靠性。因為12C晶元除了這兩根線和少量中斷線,與系統再沒有連接的線,用戶常用IC可以很容易形成標準化和模塊化,便於重複利用。

(2)I2C匯流排是一個真正的多主機匯流排,如果兩個或多個主機同時初始化數據傳輸,可以通過衝突檢測和仲裁防止數據破壞,每個連接到匯流排上的器件都有唯一的地址,任何器件既可以作為主機也可以作為從機,但同一時刻只允許有一個主機。數據傳輸和地址設定由軟體設定,非常靈活。匯流排上的器件增加和刪除不影響其他器件正常工作。

(3)I2C匯流排可以通過外部連線進行在線檢測,便於系統故障診斷和調試,故障可以立即被定址,軟體也利於標準化和模塊化,縮短開發時問。

(4)連接到相同匯流排上的IC數量只受匯流排最大電容的限制,串列的8位雙向數據傳輸位速率在標準模式下可達100Kbit/s,快速模式下可達400Kbit/s,高速模式下可達3.4Mbit/s。

(5)匯流排具有極低的電流消耗.抗高雜訊干擾,增加匯流排驅動器可以使匯流排電容擴大10倍,傳輸距離達到15m;兼容不同電壓等級的器件,工作溫度範圍寬。

發送到SDA 線上的每個位元組必須為8 位,每次傳輸可以發送的位元組數量不受限制。每個位元組后必須跟一個響應位。首先傳輸的是數據的最高位(MSB),如果從機要完成一些其他功能后(例如一個內部中斷服務程序)才能接收或發送下一個完整的數據位元組,可以使時鐘線SCL 保持低電平,迫使主機進入等待狀態,當從機準備好接收下一個數據位元組並釋放時鐘線SCL 后數據傳輸繼續。

數據傳輸必須帶響應,相關的響應時鐘脈衝由主機產生。在響應的時鐘脈衝期間發送器釋放SDA 線(高)。

在響應的時鐘脈衝期間,接收器必須將SDA 線拉低,使它在這個時鐘脈衝的高電平期間保持穩定的低電平。

通常被定址的接收器在接收到的每個位元組后,除了用CBUS 地址開頭的數據,必須產生一個響應。當從機不能響應從機地址時(例如它正在執行一些實時函數不能接收或發送),從機必須使數據線保持高電平,主機然後產生一個停止條件終止傳輸或者產生重複起始條件開始新的傳輸。

如果從機接收器響應了從機地址,但是在傳輸了一段時間后不能接收更多數據位元組,主機必須再一次終止傳輸。這個情況用從機在第一個位元組后沒有產生響應來表示。從機使數據線保持高電平,主機產生一個停止或重複起始條件。

如果傳輸中有主機接收器,它必須通過在從機發出的最後一個位元組時產生一個響應,向從機發送器通知數據結束。從機發送器必須釋放數據線,允許主機產生一個停止或重複起始條件。

所有主機在SCL線上產生它們自己的時鐘來傳輸I2C匯流排上的報文。數據只在時鐘的高電平周期有效,因此需要一個確定的時鐘進行逐位仲裁。

時鐘同步通過線與連接I2C 介面到SCL 線來執行。這就是說SCL 線的高到低切換會使器件開始數它們的低電平周期,而且一旦器件的時鐘變低電平,它會使SCL 線保持這種狀態直到到達時鐘的高電平。但是如果另一個時鐘仍處於低電平周期,這個時鐘的低到高切換不會改變SCL 線的狀態。因此SCL 線被有最長低電平周期的器件保持低電平。此時低電平周期短的器件會進入高電平的等待狀態。

當所有有關的器件數完了它們的低電平周期后,時鐘線被釋放並變成高電平。之後,器件時鐘和SCL線的狀態沒有差別,而且所有器件會開始數它們的高電平周期。首先完成高電平周期的器件會再次將SCL線拉低。

這樣產生的同步SCL 時鐘的低電平周期由低電平時鐘周期最長的器件決定,而高電平周期由高電平時鐘周期最短的器件決定。

快速模式器件可以在400kbit/s 下接收和發送。最小要求是:它們可以和400kbit/s 傳輸同步,可以延長SCL 信號的低電平周期來減慢傳輸。快速模式器件都向下兼容,可以和標準模式器件在0~100kbit/s 的I2C 匯流排系統通訊。但是,由於標準模式器件不向上兼容,所以不能在快速模式I2C 匯流排系統中工作。快速模式I2C 匯流排規範與標準模式相比有以下特徵:

1、最大位速率增加到400kbit/s;

2、調整了串列數據(SDA)和串列時鐘(SCL )信號的時序;

3、快速模式器件的輸入有抑制毛刺的功能,SDA 和SCL輸入有施密特觸發器;

4、快速模式器件的輸出緩衝器對SDA 和SCL 信號的下降沿有斜率控制功能;

5、如果快速模式器件的電源電壓被關斷,SDA 和SCL 的I/O 管腳必須懸空,不能阻塞匯流排;

6、連接到匯流排的外部上拉器件必須調整以適應快速模式I2C 匯流排更短的最大允許上升時間。對於負載最大是200pF 的匯流排,每條匯流排的上拉器件可以是一個電阻,對於負載在200pF~400pF 之間的匯流排,上拉器件可以是一個電流源(最大值3mA )或者是一個開關電阻電路。

高速模式(Hs 模式)器件對I2C 匯流排的傳輸速度有巨大的突破。Hs 模式器件可以在高達3.4Mbit/s 的位速率下傳輸信息,而且保持完全向下兼容快速模式或標準模式(F/S 模式)器件,它們可以在一個速度混合的匯流排系統中雙向通訊。

Hs 模式傳輸除了不執行仲裁和時鐘同步外,與F/S 模式系統有相同的串列匯流排協議和數據格式。

高速模式下I2C 匯流排規範如下:

1、Hs 模式主機器件有一個SDAH 信號的開漏輸出緩衝器和一個在SCLH 輸出的開漏極下拉和電流源上拉電路。這個電流源電路縮短了SCLH 信號的上升時間,任何時候在Hs 模式,只有一個主機的電流源有效;

2、在多主機系統的Hs 模式中,不執行仲裁和時鐘同步,以加速位處理能力。仲裁過程一般在前面用F/S 模式傳輸主機碼后結束;

3、Hs 模式主機器件以高電平和低電平是1:2 的比率產生一個串列時鐘信號。解除了建立和保持時間的時序要求;

4、可以選擇Hs 模式器件有內建的電橋。在Hs 模式傳輸中,Hs 模式器件的高速數據(SDAH)和高速串列時鐘(SCLH )線通過這個電橋與F/S 模式器件的SDA 和SCL 線分隔開來。減輕了SDAH 和SCLH 線的電容負載,使上升和下降時間更快;

5、Hs 模式從機器件與F/S 從機器件的唯一差別是它們工作的速度。Hs 模式從機在SCLH 和SDAH輸出有開漏輸出的緩衝器。SCLH 管腳可選的下拉晶體管可以用於拉長SCLH 信號的低電平,但只允許在Hs 模式傳輸的響應位後進行;

6、Hs 模式器件的輸出可以抑制毛刺,而且SDAH 和SCLH 輸出有一個施密特觸發器;

7、Hs 模式器件的輸出緩衝器對SDAH 和SCLH 信號的下降沿有斜率控制功能。