閂鎖效應

CMOS工藝所特有的寄生效應

閂鎖效應(Latch-up)是CMOS工藝所特有的寄生效應。

閂鎖效應是CMOS工藝所特有的寄生效應,嚴重會導致電路的失效,甚至燒毀晶元。閂鎖效應是由NMOS的有源區、P襯底、N阱、PMOS的有源區構成的n-p-n-p結構產生的,當其中一個三極體正偏時,就會構成正反饋形成閂鎖。避免閂鎖的方法就是要減小襯底和N阱的寄生電阻,使寄生的三極體不會處於正偏狀態。靜電是一種看不見的破壞力,會對電子元器件產生影響。ESD和相關的電壓瞬變都會引起閂鎖效應(latch-up),是半導體器件失效的主要原因之一。如果有一個強電場施加在器件結構中的氧化物薄膜上,則該氧化物薄膜就會因介質擊穿而損壞。很細的金屬化跡線會由於大電流而損壞,並會由於浪涌電流造成的過熱而形成開路。這就是所謂的“閂鎖效應”。在閂鎖情況下,器件在電源與地之間形成短路,造成大電流、EOS(電過載)和器件損壞。

可以通過提供大量的阱和襯底接觸來避免閂鎖效應。閂鎖效應在早期的CMOS工藝中很重要。不過,現在已經不再是個問題了。在近些年,工藝的改進和設計的優化已經消除了閂鎖的危險。

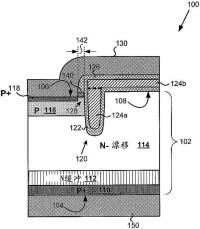

Q1為一垂直式PNP BJT,基極(base)是nwell,基極到集電極(collector)的增益可達數百倍;Q2是一側面式的NPN BJT,基極為P substrate,到集電極的增益可達數十倍;Rwell是nwell的寄生電阻;Rsub是substrate電阻。

原理示意圖

1、晶元一開始工作時VDD變化導致nwell和P substrate間寄生電容中產生足夠的電流,當VDD變化率大到一定地步,將會引起Latch up。

3、ESD靜電加壓,可能會從保護電路中引入少量帶電載子到well或substrate中,也會引起SCR的觸發。

4、當很多的驅動器同時動作,負載過大使power和gnd突然變化,也有可能打開SCR的一個BJT。

5、Well側面漏電流過大。

1、在基體(substrate)上改變金屬的摻雜,降低BJT的增益

2、避免source和drain的正向偏壓

3、增加一個輕摻雜的layer在重摻雜的基體上,阻止側面電流從垂直BJT到低阻基體上的通路

4、使用Guard ring:P+ring環繞nmos並接GND;N+ring環繞pmos並接VDD,一方面可以降低Rwell和Rsub的阻值,另一方面可阻止載流子到達BJT的基極。如果可能,可再增加兩圈ring。

5、Substrate contact和well contact應盡量靠近source,以降低Rwell和Rsub的阻值。

7、除在I/O處需採取防Latch up的措施外,凡接I/O的內部mos也應圈guard ring。

8、I/O處盡量不使用pmos(nwell)

CMOS電路由於輸入太大的電流,內部的電流急劇增大,除非切斷電源,電流一直在增大這種效應就是鎖定效應。當產生鎖定效應時,CMOS的內部電流能達到40mA以上,很容易燒毀晶元。

1)在輸入端和輸出端加鉗位電路,使輸入和輸出不超過規定電壓。

2)晶元的電源輸入端加去耦電路,防止VDD端出現瞬間的高壓。

3)在VDD和外電源之間加限流電阻,即使有大的電流也不讓它進去。

4)當系統由幾個電源分別供電時,開關要按下列順序:開啟時,先開啟CMOS電路的電源,再開啟輸入信號和負載的電源;關閉時,先關閉輸入信號和負載的電源,再關閉CMOS電路的電源。