MIPS架構

採取精簡指令集的處理器架構

MIPS架構(英語:MIPS architecture,為Microprocessor without interlocked piped stages architecture的縮寫,亦為Millions of Instructions Per Second的雙關語),是一種採取精簡指令集(RISC)的處理器架構,1981年出現,由MIPS科技公司開發並授權,廣泛被使用在許多電子產品、網路設備、個人娛樂裝置與商業裝置上。最早的MIPS架構是32位,最新的版本已經變成64位。

MIPS架構20多年前由斯坦福大學開發,是一種簡潔、優化、具有高度擴展性的RISC架構。它的基本特點是:包含大量的寄存器、指令數和字元、可視的管道延時時隙,這些特性使MIPS架構能夠提供最高的每平方毫米性能和當今SoC設計中最低的能耗。

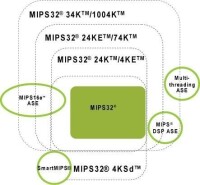

MIPS特定應用擴展

特定應用擴展(Application Specific Extension,ASE),可提升特定類型應用的性能,其包括:

業界標準MIPS32® 和 MIPS64®架構的MIPS® DSP ASE信號處理擴展,能夠提升客戶SoC的媒體性能。

SmartMIPS® ASE,可在智能卡及其它安全數據應用中實現前所未有的安全性。

MIPS16e™ 代碼壓縮 ASE,能減少多達40%的存儲器使用量。

MIPS-3D® ASE,可在數字娛樂和多媒體產品中實現高性能三維圖像處理的一種具成本效益的解決方案。

MIPS32®架構刷新了32位嵌入式處理器的性能標準。它是MIPS科技公司下一代高性能MIPS-Based™處理器SoC發展藍圖的基礎,並向上兼容MIPS64®64位架構。MIPS架構擁有強大的指令集、從32位到64位的可擴展性、廣泛的軟體開發工具以及眾多MIPS科技公司授權廠商的支持,是領先的嵌入式架構。MIPS32架構是以前的MIPS I™ 和 MIPS II™指令集架構(ISA)的擴展集,整合了專門用於嵌入式應用的功能強大的新指令,以及以往只在64位R4000™ 和 R5000® MIPS®處理器中能見到的已經驗證的存儲器管理和特權模式控制機制。通過整合強大的新功能、標準化特權模式指令以及支持前代ISA,MIPS32架構為未來所有基於32位MIPS的開發提供了一個堅實的高性能基礎。

MIPS32架構從流行的R4000/R5000類64位處理器衍生出特權模式異常處理和存儲器管理功能。它採用一組寄存器來反映緩存器、MMU、TLB及各個內核中實現的其它特權功能的配置。通過對特權模式和存儲器管理進行標準化,並經由配置寄存器提供信息,MIPS32架構能夠使實時操作系統、其它開發工具和應用代碼同時被執行,並在MIPS32 和MIPS64處理器系列的各個產品之間復用。

由於增加了密集型數據處理、數據流和斷言操作(predicated operations) ,可滿足嵌入式市場不斷增長的計算需求。條件數據移動(Conditional data move)和數據緩存預取(prefetch)指令被引入,以期提高通信及多媒體應用的數據吞吐量。固定浮點DSP型指令可進一步增強多媒體處理能力。這些新指令,包括乘法、乘加、乘減和“前導計數(count leading)0s/1s”,在處理音頻、視頻和多媒體等數據流時,無需在系統中增加額外的DSP硬體即可提供更高的性能。功能強大的浮點指令可加快某些任務的執行速度,比如一些DSP演演算法的處理、圖形操作的實時計算。浮點操作可選擇軟體模擬。最後,為簡化系統集成任務,MIPS32標準定義EJTAG(增強型JTAG)選項功能作為非入侵式、片上實時調試系統。

MIPS64®架構刷新了64位MIPS-Based™嵌入式處理器的性能標準。它代表著下一代高性能MIPS®處理器的基礎,併兼容MIPS32®32位架構。MIPS架構擁有強大的指令集、從32位到64位的可擴展性、廣泛可獲得的軟體開發工具以及眾多MIPS科技公司授權廠商的支持,是領先的嵌入式架構。MIPS64架構是以前的MIPS IV™ 和 MIPS V™指令集架構(ISA)的擴展集,整合了專門用於嵌入式應用的功能強大的新指令,以及以往在R4000® 和 R5000® MIPS處理器中執行的已經驗證的存儲器管理和特權模式控制機制。通過整合強大的新功能、標準化特權模式指令、支持前代ISA,以及提供從MIPS32架構升級的路徑,MIPS64架構為未來基於MIPS處理器的開發提供了一個堅實的高性能基礎。

MIPS64架構基於一種固定長度的定期編碼指令集,並採用導入/存儲(load/store)數據模型。經改進,這種架構可支持高級語言的優化執行。其算術和邏輯運算採用三個操作數的形式,允許編譯器優化複雜的表達式。此外,它還帶有32個通用寄存器,讓編譯器能夠通過保持對寄存器內數據的頻繁存取進一步優化代碼的生成性能。

這種架構從R4000/R5000類處理器衍生出特權模式異常處理和存儲器管理功能。它採用一組寄存器來反映緩存器、MMU、TLB及各個內核中實現的其它特權功能的配置。MIPS32架構的兼容模式讓32位代碼無需修改即可在MIPS64上運行。通過提供後向兼容性、對特權模式和存儲器管理進行標準化,並經由配置寄存器提供信息,MIPS64架構能夠使實時操作系統和應用代碼同時被執行,並在MIPS32和MIPS64處理器系列的各個產品之間復用。

高性能緩存器及存儲器管理方案的靈活性仍繼續成為MIPS架構的一大優勢。MIPS64架構利用定義良好的緩存控制選項功能進一步擴展了這種優勢。指令和數據緩存器的大小可以從256byte到4Mbyte。數據緩存可採用回寫或直寫策略。無緩存也是可選配置。存儲器管理機制可以採用TLB或塊地址轉換(BAT)策略。利用TLB,MIPS64架構可滿足Windows CE和Linux的存儲器管理要求。

由於增加了數據流和斷言操作(predicated operations),可滿足嵌入式市場不斷增長的計算需求。條件數據移動和數據預取指令被標準化,以提高通信及多媒體應用的系統級數據吞吐量。

固定浮點DSP型指令可進一步增強多媒體處理能力。這些以前只有在某些64位MIPS處理器上才使用的指令,包括乘法(MUL)、乘加(MADD)、乘減(MSUB)和“前導計數(count leading) 0s/1s”,在處理音頻、視頻和多媒體等數據流時,無需在系統中增加額外的DSP硬體即可提供更高的性能。

功能強大的64位浮點寄存器和執行單元可加快某些任務的執行速度,比如一些DSP演演算法的處理、圖形操作的實時計算。雙單精度指令(Paired-Single instruction)在一個64位寄存器中裝入了兩個32位浮點操作數,從而實現單指令多數據操作(SIMD)。這種方法的執行速度是傳統32位浮點單元的兩倍。浮點操作可選擇軟體模擬。

MIPS64架構兼具32位和64位定址模式,同時採用64位數據工作。這樣一來,無需額外的存儲器進行64位定址就能獲得64位數據的優勢。為了便於從32位系列的移植,該架構還帶有32位兼容模式,在這種模式中,所有寄存器和地址都是32位寬,MIPS32架構中出現的所有指令都被執行。

microMIPS™是一種在單個統一的指令集架構中集成了16位和32位優化指令的高性能代碼壓縮技術。它支持MIPS32® 和MIPS64® Release 2架構,整合了可變長度重新編碼MIPS指令集和新增的代碼量優化16位和32位指令,可提供高性能和高代碼密度。

microMIPS是一個完整的ISA,既能單獨工作,也能與原有的MIPS32兼容指令解碼器共同工作,允許程序混合16位和32位代碼,無需模式切換。microMIPS的程序代碼量較小,因此可獲得更好的緩存利用率和更小的取指帶寬(fetch bandwidth),從而有助於提升性能,降低功耗。

microMIPS包含所有MIPS ASE指令,支持CorExtend™/UDI介面。而且,針對microMIPS軟體及系統開發,MIPS科技公司與第三方合作夥伴生態系統提供有一套全面完善的軟硬體工具支持。新推出的M14K™和 M14Kc™是首先執行 microMIPS的處理器內核。

1984年,約翰·軒尼詩教授離開斯坦福大學,創立MIPS科技公司。於1985年,設計出R2000晶元,1988年,將其改進為R3000晶元。

2002年,中國科學院計算所開始研發龍芯處理器,採用MIPS架構,但未經MIPS公司的授權,遭到侵權的控告。

2009年,中國科學院與MIPS公司達成和解,得到正式授權。