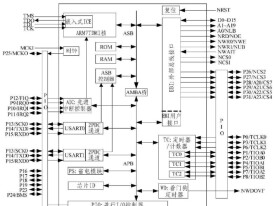

隨著深亞微米工藝技術日益成熟,集成電路晶元的規模越來越大。數字IC從基於時序驅動的設計方法,發展到基於IP核復用的設計方法,並在SOC設計中得到了廣泛應用。在基於IP核復用的SoC(System on Chip的縮寫,稱為系統級晶元,也有稱片上系統)設計中,片上匯流排設計是最關鍵的問題。為此,業界出現了很多片上匯流排標準。其中,由ARM公司推出的AMBA片上匯流排受到了廣大IP開發商和SoC系統集成者的青睞,已成為一種流行的工業標準片上結構。AMBA規範主要包括了AHB(Advanced High performance Bus)系統匯流排和APB(Advanced Peripheral Bus)外圍匯流排。

AHB=Advanced High Performance Bus,譯作高級高性能匯流排。如同USB(Universal Serial Bus)一樣,也是一種匯流排介面。

AHB

AHB主要用於高性能模塊(如

CPU、

DMA和

DSP等)之間的連接,作為

SoC的片上系統匯流排,它包括以下一些特性:單個時鐘邊沿操作;非三態的實現方式;支持突發傳輸;支持分段傳輸;支持多個主控制器;可配置32位~128位匯流排寬度;支持

位元組、半字和字的傳輸。AHB系統由主模塊、從模塊和基礎結構 (Infrastructure)3部分組成,整個AHB匯流排上的傳輸都由主模塊發出,由從模塊負責回應。基礎結構則由

仲裁器(arbiter)、主模塊到從模塊的多路器、從模塊到主模塊的多路器、

解碼器(decoder)、虛擬從模塊(dummy Slave)、虛擬主模塊(dummy Master)所組成。其互連結構如圖1所示。針對

Soc設計中IP復用問題提出了一種新的解決辦法。傳統的方法是將特定功能模塊的非標準介面標準化為AHB主/從設備介面。本文提出了一種新的基於

ARM的Soc通用平台設計

寄存器匯流排標準介面,這種設計使整個系統的結構清晰,增強系統的通用性與系統中功能模塊的可移植性。

AHB的模擬波形

AMBA2.0規範包括四個部分:AHB、

ASB、APB和Test Methodology。AHB的相互連接採用了傳統的帶有主模塊和從模塊的共享匯流排,介面與互連功能分離,這對晶元上模塊之間的互連具有重要意義。AMBA已不僅是一種匯流排,更是一種帶有介面模塊的互連體系。

APB主要用於低帶寬的周邊外設之間的連接,例如UART、1284等,它的匯流排架構不像AHB支持多個主模塊,在APB裡面唯一的主模塊就是APB橋。其特性包括:兩個時鐘周期傳輸;無需等待周期和回應信號;控制邏輯簡單,只有四個控制信號。

1)系統初始化為IDLE狀態,此時沒有傳輸操作,也沒有選中任何從模塊。2)當有傳輸要進行時,PSELx=1,PENABLE=0,系統進入SETUP狀態,並只會在SETUP狀態停留一個周期。當PCLK的下一個上升沿時到來時,系統進入

ENABLE狀態。

3)系統進入ENABLE狀態時,維持之前在SETUP狀態的PADDR、PSEL、

PWRITE不變,並將PENABLE置為1。傳輸也只會在ENABLE狀態維持一個周期,在經過SETUP與ENABLE狀態之後就已完成。之後如果沒有傳輸要進行,就進入IDLE狀態等待;如果有連續的傳輸,則進入SETUP狀態。

AHB

大多數掛在匯流排上的模塊(包括處理器)只是單一屬性的功能模塊:主模塊或者從模塊。主模塊是向從模塊發出讀寫操作的模塊,如CPU,DSP等;從模塊是接受命令並做出反應的模塊,如片上的

RAM,AHB/APB橋等。另外,還有一些模塊同時具有兩種屬性,例如直接存儲器存取(DMA)在被編程時是從模塊,但在系統讀傳輸數據時必須是主模塊。如果匯流排上存在多個主模塊,就需要仲裁器來決定如何控制各種主模塊對匯流排的訪問。雖然仲裁規範是AMBA匯流排規範中的一部分,但具體使用的演演算法由RTL設計工程師決定,其中兩個最常用的演演算法是固定優先順序演演算法和循環制演演算法。AHB匯流排上最多可以有16個主模塊和任意多個從模塊,如果主模塊數目大於16,則需再加一層結構(具體參閱ARM公司推出的Multi-layer AHB規範)。APB橋既是APB匯流排上唯一的主模塊,也是AHB系統匯流排上的從模塊。其主要功能是鎖存來自AHB系統匯流排的地址、數據和控制信號,並提供二級解碼以產生APB外圍設備的選擇信號,從而實現AHB協議到APB協議的轉換。