共找到2條詞條名為解碼器的結果 展開

- 多輸入多輸出組合邏輯電路器件

- 編譯器

解碼器

多輸入多輸出組合邏輯電路器件

解碼器(decoder)是一類多輸入多輸出組合邏輯電路器件,其可以分為:變數解碼和顯示解碼兩類。變數解碼器一般是一種較少輸入變為較多輸出的器件,常見的有n線-2^n線解碼和8421BCD碼解碼兩類;顯示解碼器用來將二進位數轉換成對應的七段碼,一般其可分為驅動LED和驅動LCD兩類。

解碼是編碼的逆過程,在編碼時,每一種二進位代碼,都賦予了特定的含義,即都表示了一個確定的信號或者對象。把代碼狀態的特定含義“翻譯”出來的過程叫做解碼,實現解碼操作的電路稱為解碼器。或者說,解碼器是可以將輸入二進位代碼的狀態翻譯成輸出信號,以表示其原來含義的電路。

解碼器

解碼器

二進位碼解碼器,也稱最小項解碼器,N中取一解碼器,最小項解碼器一般是將二進位碼譯為十進位碼;

代碼轉換解碼器,是從一種編碼轉換為另一種編碼;

顯示解碼器,一般是將一種編碼譯成十進位碼或特定的編碼,並通過顯示器件將解碼器的狀態顯示出來。

變數解碼器是一個將n個輸入變為2^n個輸出的多輸出端的組合邏輯電路。其模型可用下圖來表示,其中輸入變化的所有組合中,每個輸出為1的情況僅一次,由於最小項在真值表中僅有一次為1,所以輸出端為輸入變數的最小項的組合。故解碼器又可以稱為最小項發生器電路。

解碼器是一種具有“翻譯”功能的邏輯電路,這種電路能將輸入二進位代碼的各種狀態,按照其原意翻譯成對應的輸出信號。有一些解碼器設有一個和多個使能控制輸入端,又成為片選端,用來控制允許解碼或禁止解碼。

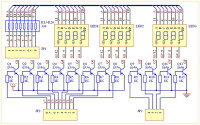

在圖1中,74138是一種3線—8線解碼器,三個輸入端CBA共有8種狀態組合(000—111),可譯出8個輸出信號Y0—Y7。這種解碼器設有三個使能輸入端,當G2A與G2B均為0,且G1為1時,解碼器處於工作狀態,輸出低電平。當解碼器被禁止時,輸出高電平。

圖2時檢測74ls138解碼器時間波形的電路,使用的虛擬儀器為數字信號發生器和邏輯分析儀。數字信號發生器在一個周期內按順序送出兩組000—111的方波信號。

圖3表明如何將兩片3線—8線解碼器連接成4線—16線解碼器。其中第二片74138的使能端G1和第一片的使能端G2A接成D輸入端。當D=0時,第一片74138工作,對0000—0111的輸入信號進行解碼輸出。當D=1時,第二片74138工作,對1000—1111的輸入信號進行解碼輸出。

在圖4中,7442為二—十進位解碼器,具有4個輸入端和10個輸出端。輸入信號採用8421BCD碼,二進位數0000—1001與十進位數0—9對應。當輸入超過這個範圍是無效,10個輸出端均為高電平。7442電路沒有使能端,因此只要輸入在規定範圍內,就會有一個輸出端為低電平。

圖5位BCD—七段顯示解碼器電路,LED數碼管將顯示與BCD碼對應的十進位數0—9。因為顯示解碼器電路輸出高電平,所以應該採用共陰極LED數碼管。

編碼與解碼的過程剛好相反。通過編碼器可對一個有效輸入信號生成一組二進位代碼。有的編碼器設有使能端,用來控制允許編碼或禁止編碼。

優先編碼器的功能是允許同時在幾個輸入端有輸入信號,編碼器按輸入信號排定的優先順序,只對同時輸入的幾個信號中優先權最高的一個進行編碼。在圖6中,74147為BCD優先編碼器,輸入和輸出都是低電平有效。為了取得有效輸出高電平,可在每個輸出端連接一個反相器。7417隻有1—9各輸入端,0輸入端不接入電路。這是因為7417約定,當無有效輸入時,輸出0的BCD代碼0000。

圖7是一個檢測優先編碼/解碼功能的邏輯電路,對每一個接地的邏輯開關,數碼管都會顯示一個相應的十進位數。在輸入端的8個邏輯開關中,代號為[7]的優先順序別最高,代號為[0]的優先順序別最低。

解碼器

圖1

在討論解碼器的功能前我們來看一下解碼器的內部結構,下圖是一個主要由與門電路構成的2輸入解碼器,其輸出共有22個(即4),從圖上可以每個其輸出對應於一個最小項。在這電路中當輸入BA的取值為10,即對應於十進位數的2時,其F2輸出為高電平,其餘的輸出為0。

圖2

下圖同樣是一個2輸入的解碼器,但由於其主要使用了與非門構成的,其每個輸出對應於一個最小項的非。在這電路中,當輸入BA的取會為10時,其輸出F2不再為1,而是輸出為0,其餘的輸出為1。

我們將下面這種解碼器電路看作輸出低電平有效(即當輸入變數對應於十進位i時,其對應的第i個輸出端為低電平,其餘為高電平)。而前面的解碼器當然就是高電平有效了。

圖3

上面列出的兩個電路為2輸入的情況,對於輸入為2個以上的情況也與此相同,同樣可以有輸出高電平有效的,也有輸出低電平有效的。

由於任何一組合邏輯電路都可以寫成最小項表達式的形式,而解碼器電路的輸出列出了該電路的所有最小項表達式(或最小項的非表達式),故我們可能用解碼器電路實現各種組合邏輯電路。

例 用解碼電路實現F(X,Y,Z)=∑(0,1,4,6,7)=∏M(2,3,5)

我們實現該邏輯功能可以有幾種方法,下圖列出了四種方法,從這四個圖中你應可以總結出其規律。

其中:

圖a為高電平有效輸出加或門的實現方法;

圖b為低電平有效輸出加與非門的實現方法;

圖c為高電平有效輸出加或非門的實現方法;

圖d為低電平有效輸出加與非門的實現方法;

圖4

在中規模集成電路中經常會碰到使能端(Enable Pin),使能端可以是輸入,也可以是輸出,其是用來擴展中規模集成電路功能的輸入/輸出端,下圖a是一個2輸入解碼器上加上一個輸入E,由於輸入端E的加入,其功能發生了變化,當E=0時,其輸出全部為0,而該解碼器在沒有加上E端時,其為高電平有效,這時其輸出端沒有一個處於有效工作狀態,我們可以理解為E=0時,該解碼器不工作;當E=1時,我們看到,其解碼器可以正常工作,我們把這種輸入端在E=1時能正常工作的使能端叫做高電平有效。下圖b為其簡化的邏輯符號。

圖5

下圖是使用使能端將兩個2輸入的解碼器轉變為3輸入的解碼器的例子,在下圖中當I2為低電平時,第1個解碼器的使能端為高電平,其正常工作,而第2個解碼器此時不工作,於是解碼器1的輸出對應於輸入I3I2I1的0~3;當I2為高電平時,解碼器2工作,而解碼器1不工作,故其輸出對應於輸入I2I1I0的4~7,故下圖電路實現了利用使能端將2輸入的解碼器擴展為3輸入的解碼器。

圖6

在中規模集成電路中解碼器有幾種型號,使用最廣的通常是74138,其是一個3到8的解碼器,下圖是其邏輯符號及管腳排布,下表中列出了該器件的邏輯功能,從表中可以看出其輸出為低電平有效,使能端G1為高電平有效,/G2,/G3為低電平有效,當其中一個為低電平,輸出端全部為1。

圖7

例 試用74138實現函數F(X,Y,Z)=∑m(0,2,4,7)

用74138實現函數與前面講到的解碼器實現邏輯函數的方法相同,但須注意兩點:

1.74138的輸出是低電平有效,故實現邏輯功能時,輸出端不可接或門及或非門(因為每次僅一個為低電平,其餘皆為高電平);

2.74138與前面不同的是,其有使能端,故使能端必須加以處理,否則無法實現需要的邏輯功能。下圖給出了其最終的電路。

圖8

顯示解碼

在數字系統中常見的數碼顯示器通常有:發光二極體數碼管(LED數碼管)和液晶顯示數碼管(LCD數碼管)兩種。發光二極體數碼管是用發光二極體構成顯示數碼的筆劃來顯示數字,由於發二極體會發光,故LED數碼管適用於各種場合。液晶顯示數碼管是利用液晶材料在交變電壓的作用下晶體材料會吸收光線,而沒有交變電場作用下有筆劃不會聽吸光,這樣就可以來顯示數碼,但由於液晶材料須有光時才能使用,故不能用於無外界光的場合(現在攜帶型電腦的液晶顯示器是用背光燈的作用下可以在夜間使用),但液晶顯示器有一個最大的優點就是耗電相當節省,所以廣泛使用於小型計算器等小型設備的數碼顯示。

下圖是LED數碼管的內部結構及顯示數碼的情況,其是一個陽極連在一體的一種LED數碼管,我們通常稱為共陽極數碼管。既然有共陽數碼管,那麼就有共陰數碼管,這裡沒有畫出其內部結構,請你自行畫一下。

圖9

發光二極體點亮只須使其正嚮導通即可,根據LED的公共極是陽極還是陰極分為兩類解碼器,即針對共陽極的低電平有效的解碼器;針對共陰極LED的高電平輸出有效的解碼器。

4511是輸出高電平有效的CMOS顯示解碼器,其輸入為8421BCD碼,下圖和表分別4511的管腳排布、邏輯符號和邏輯功能表。

圖10

圖中:

/LT:試燈極,低電平有效,當其為低電平時,所有筆劃全部亮,如不亮表示該筆劃有問題;

/BL:滅燈極,低電平有效,當其為低電平時,不管輸入的數據狀態如何,其輸出全為低電平,即所有筆劃熄滅;

/ST/LE:選通/鎖存極,其是一個復用的功能端,當輸入為低電平時,其輸出與輸入的變數有關;當輸入為高電平時,其輸出僅與該端為高電平前的狀態,並且輸入DCBA端不管如何變化,其顯示數值保持不變。

D,C,B,A:8421BCD碼輸入,其D位為最位;

a~g:輸出端,為高電平有效,故其輸出應與其陰極的數碼管相對應。

LCD解碼驅動器電路與LED的解碼驅動電路不同,其輸出不是高電平或低電平,而是脈衝電壓,當輸出有效時,其輸出為交變的脈衝電壓,否則為高電平或低電平。