cortex-a5

能效高、成本低的處理器

ARM Cortex™-A5 處理器是能效最高、成本最低的處理器,能夠向最廣泛的設備提供 Internet 訪問:從入門級智能手機、低成本手機和智能移動設備到普遍採用的嵌入式、消費類和工業設備。

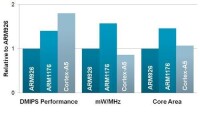

Cortex-A5 處理器可為現有 ARM926EJ-S™ 和 ARM1176JZ-S™ 處理器設計提供很有價值的遷移途徑。它可以獲得比 ARM1176JZ-S 更好的性能,比 ARM926EJ-S 更好的功效和能效以及 100% 的 Cortex-A 兼容性。

這些處理器向特別注重功耗和成本的應用程序提供高端功能,其中包括:

• 多重處理功能,可以獲得可伸縮、高能效性能

• 用於媒體和信號處理的可選浮點或 NEON™ 單元

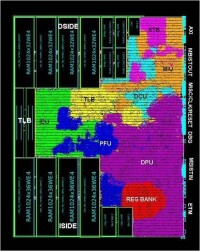

• 高性能內存系統,包括高速緩存和內存管理單元

Cortex-A5 是為以下應用領域而設計的:需要在極低功耗情況下對高級操作系統進行虛擬內存管理。

| 產品類型 | 應用 |

| 移動 | 入門級智能手機、特色手機、移動支付、音頻 |

| 家庭/消費 | 數字電視、DVD |

| 嵌入式/工業 | MPU、智能儀錶 |

提供完全 Internet 訪問功能的能效最高的應用型處理器

行業領先的能效是指 Cortex-A5 可以每單位能量完成更多的工作,這意味著可以延長移動設備的電池壽命,減少散熱。

Cortex-A5 是最小的 Cortex-A 處理器。

小尺寸:

• 降低製造成本

• 允許更多低成本集成

• 減少泄漏

cortex-a5

Cortex-A5 處理器在指令以及功能方面與更高性能的 Cortex-A8、Cortex-A9 和 Cortex-A15 處理器完全兼容 – 一直到操作系統級別。Cortex-A5 處理器還保持與經典 ARM 處理器(包括 ARM926EJ-S、ARM1176JZ-S 和 ARM7TDMI®)的向後應用程序兼容性。

| ARM Cortex-A5 性能、功耗和面積 | ||

| TSMC 40LP | TSMC 40G | |

| 工藝類型/額定電壓 | 低泄漏,1.1V | 性能,1.0V |

| 性能或頻率優化 | 頻率 | 頻率 |

| 頻率 | 530~600 MHz(所有 RVt) 700MHz + 使用 LVt | >1GHz |

| 面積,不包括 RAM/高速緩存 | 0.27mm² | 0.27mm² |

| 面積(帶 16K/16K 高速緩存) | 0.53mm² | 0.53mm² |

| 面積(帶 16K/16K 高速緩存 + NEON ) | 0.68mm² | 0.68mm² |

| 動態功耗 | 0.12 mW/MHz | <0.08mW/MHz |

| 能效 | 13 DMIPS/mW | >20 DMIPS/mW |

內核面積、頻率範圍和功耗主要取決於工藝、庫和優化情況。

上面引述的數字說明了使用通用工藝技術、ARM 標準單元庫和 RAM 的合成內核的性能。

ARM 高性能 SC12 邏輯庫和性能 RAM

頻率優化

85% 使用率

慢硅/Vdd-10% (1.0V)/125C 情況下的頻率

10% OCV 和 50ps 時鐘偏差

標準硅/Vdd (1.1V)/25C 情況下的功耗

所有額定電壓晶體管

cortex-a5

| Cortex-A5 | |

| 架構 | ARMv7-A Cortex |

| Dhrystone 性能 | 每個內核 1.57 DMIPS/MHz |

| 多核 | 1-4 個內核 還提供單核版本 |

| ISA 支持 | ARM Thumb®-2 / Thumb DSP 和 SIMD 擴展 VFPv4 浮點(可選) NEON™ 高級 SIMD(可選) Jazelle® DBX 和 RCT |

| 內存管理 | ARMv7 內存管理單元 |

| 調試和跟蹤 | CoreSight™ DK-A5 |

| Cortex-A5 主要功能 | |

| Thumb-2 技術 | 可為傳統 ARM 代碼提供最高性能,對於存儲指令佔用的內存,最多可節省 30% 的空間 |

| TrustZone® 技術 | 確保安全應用的可靠實現,適合從數字版權管理到電子支付等應用。獲得技術和行業合作夥伴的廣泛支持。 |

| NEON 媒體處理引擎 (MPE) | 可選 Cortex-A5 NEON 可提供 Cortex-A5 浮點單元的性能和功能以及 ARM NEON 高級 SIMD 指令集實現,以便進一步提高媒體和信號處理功能的速度 MPE 擴展 Cortex-A5 浮點單元 (FPU),提供一個附加寄存器集,在 8 位、16 位和 32 位整型以及 32 位浮點數據類型的基礎上支持一組豐富的 SIMD 操作。 |

| 浮點單元 (FPU) | |

| Jazelle RCT 和 DBX 技術 | 最多可使即時生產 (JIT) 和提前編譯的位元組碼語言的代碼大小縮小 3 倍,同時還支持 Java 指令的直接位元組碼執行,以便提高傳統虛擬機的速度 |

| 可配置 L1 高速緩存 | 可在 4-64K 範圍內單獨配置功率優化的 L1 指令和數據高速緩存。提供了 ARM SRAM 的優化實例。 |

| 高性能AXI匯流排 | Cortex-A5 實現支持多個未決事務的 64 位統一 AXI 匯流排,具有超過 ARM1176JZ-S 的 3 倍內存帶寬。 |

| 先進的多核技術 | |

| 偵測控制單元 (SCU) | SCU 是 ARM 多核技術的中央智能單元,負責管理互連、仲裁、通信、高速緩存之間的傳輸和系統內存傳輸、高速緩存一致性以及支持所有多核技術的處理器的其他功能。 Cortex-A5 MPCore 處理器也向其他系統加速器和非緩存 DMA 驅動的主外設公開這些功能,以便通過共享對處理器高速緩存層次結構的訪問來提高性能並降低系統範圍內的功耗。這一系統一致性還可降低在各個操作系統驅動程序中維持軟體一致性所涉及的軟體複雜性。 |

| 加速器一致性埠 (ACP) | SCU 上的此 AMBA® 3 AXI™ 兼容的輔助介面為各種系統主機提供了一個互連點,出於總體系統性能、功耗或軟體簡化的原因,這些介面更易於直接連接 Cortex-A5 MPCore 處理器。 該介面可用作標準的 AMBA 3 AXI 輔助介面,它支持所有標準讀寫事務,而對連接的組件沒有任何其他一致性要求。不過,針對一致的內存區域的任何讀事務都會與 SCU 交互,以測試所需信息是否已存儲在處理器的 L1 高速緩存內。如果存儲在其中,則會將其直接返回到請求組件。如果未存儲在 L1 高速緩存中,則在最後轉發到主內存之前還有機會存儲在 L2 高速緩存中。 對於針對任何一致的內存區域的寫事務,在將寫入數據轉發到內存系統之前,SCU 會強制其保持一致性。此外,此事務還可分配到 L2 高速緩存,從而消除直接寫入對晶元外內存產生的功率和性能影響。 |

| 通用中斷控制器 (GIC) | 實現最近標準化的、基於架構的 ARM 中斷控制器后,GIC 提供了一種強大且靈活的方式,用來進行處理器間通信以及路由系統中斷和確定其優先次序。在軟體控制下,最多支持 224 次獨立中斷,每次中斷均可在 CPU 之間分佈,經過硬體確定優先順序,然後在操作系統和 TrustZone 軟體管理層之間路由。藉助半虛擬化管理器,此路由靈活性以及支持虛擬化操作系統中斷這一特性賦予了增強解決方案功能所需的其中一個主要功能。 |

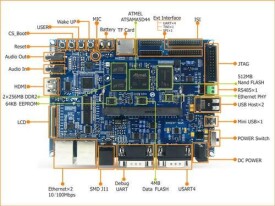

米爾科技基於ATMEL SAMA5D3X系列晶元的 MYD-SAMA5D3X系列開發板,基於ARM Cortex-A5內核,536MHz主頻,512MB內核及256MB Nandflash,系列含MYD-SAMA5D31開發板、MYD-SAMA5D33開發板、MYD-SAMA5D34開發板、MYD-SAMA5D35開發板共4個。