浮點處理器

浮點處理器

在計算機科學中,浮點(floating point)是一種對於實數的近似值數值表現法,由一個有效數字(即尾數)加上冪數來表示,通常是乘以某個基數的整數次指數得到。浮點處理器是指專門用於處理浮點運算的處理器,在大多數計算機中,浮點處理器是協處理器。

浮點處理器是指計算機中用於處理浮點數運算的處理器,在大多數情況下,浮點處理器只是作為輔助處理器,完成中央處理器完成其無法執行或執行效率、效果低下的處理工作。在科學計算中,由於大部分計算都是浮點數運算,這時浮點處理器可以加快運算速度和提高系統執行效率,這時的浮點處理器一般也稱作定製處理器。

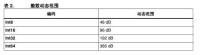

整數動態範圍

浮點數動態範圍

由於浮點運算適合兩個數之間的任何運算,因此它需要非常多的資源。例如,我們需要:

對齊兩個數值(使兩個數值的指數相同)執行運算;舍入結果;對結果進行編碼。

在沒有 FPU 的處理器上,這些運算全部由軟體通過 C 編譯器庫完成,並且對程序員不可見;但這樣做性能非常低。在有 FPU 的處理器上,對於大部分指令而言,所有運算都由硬體在單個周期內完成。C 編譯器不使用其自身的浮點庫,但會直接生成 FPU 原生指令。

在有 FPU 的處理器上執行數學演演算法時,程序員不必在性能和開發時間之間做出選擇。利用FPU,可以通過 matlab 或 scilab 等高級工具直接可靠地使用任何生成的代碼,同時確保實現性能。

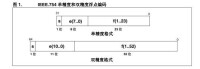

IEEE.754 單精度和雙精度浮點編碼

數值格式

所有值均由三個域組成:

符號:s

偏置指數:

— 指數之和 = e

— 常數值 = 偏置值

小數(或尾數):f

可以使用各種長度對值進行編碼:

16 位:半精度格式

32 位:單精度格式

64 位:雙精度格式

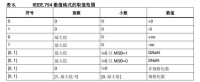

IEEE 定義了五類不同的數:

規格化數:標準浮點數

IEEE.754 數值格式的取值範圍

零:零值加上符號用於表示飽和運算(正或負)。指數和小數均為空。

無窮大:無窮大值加上符號用於表示 +∞ 或 -∞。溢出或除以 0 時會產生無窮大值。指數設置為其最大

值,尾數為空。

NaN(非數字):NaN 用於表示不明確的運算結果,例如 0/0 或負數的平方根。指數設置為其最大值,尾數不為空。尾數的 MSB 用於判斷該值是 QNaN(可通過後續運算傳播)還是 SNaN(生成錯誤)。

舍入模式

該標準定義了以下四種主要舍入模式:

最近舍入

向 +∞ 舍入

向 -∞ 舍入

向 0 舍入

最近舍入是默認的舍入模式(最常用)。如果與兩個最近值的距離相等,則選擇 LSB 等於 0的值。舍入模式會改變算數運算的結果,因此非常重要。可以通過 FPU 配置寄存器更改舍入模式。

異常和異常處理

該標準支持 5 種異常:

無效運算:運算結果為 NaN

除以零

上溢:根據舍入模式,運算結果為 +/-∞ 或 +/-最大值

下溢:運算結果為非規格化數

結果不準確:由舍入所致

可用兩種方式處理異常:

可以生成陷阱。陷阱處理程序會返回要使用的值來替代異常結果。

可以生成中斷。中斷處理程序不能返回要使用的值來替代異常結果。

為了提高計算機運算速度,用來彌補微處理器在數值計算方面不足的浮點運算部件。是微處理器的一種。是一種協助中央處理器完成其無法執行或執行效率、效果低下的處理工作而開發和應用的處理器。這種中央處理器無法執行的工作有很多,比如設備間的信號傳輸、接入設備的管理等;而執行效率、效果低下的有圖形處理、聲頻處理等。為了進行這些處理,各種輔助處理器就誕生了。整數運算器與浮點運算器已經集成在一起,因此浮點處理器已經不算是輔助處理器。而內建於CPU中的協處理器,同樣不算是輔助處理器,除非它是獨立存在。