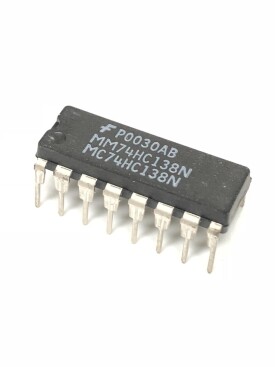

74HC138

高速CMOS器件

74HC138是一款高速CMOS器件,74HC138引腳兼容低功耗肖特基TTL(LSTTL)系列。74HC138解碼器可接受3位二進位加權地址輸入(A0, A1和A2),併當使能時,提供8個互斥的低有效輸出(Y0至Y7)。

74HC138特有3個使能輸入端:兩個低有效(E1和E2)和一個高有效(E3)。除非E1和E2置低且E3置高,否則74HC138將保持所有輸出為高。

封裝引腳 、、、

複合,僅需片晶元反相器,即可輕鬆實現并行擴展,組合成為一個1-32(5線到32線)解碼器。任選一個低有效使能輸入端作為數據輸入,而把其餘的使能輸入端作為選通端,則74HC138亦可充當一個8輸出多路分配器,未使用的使能輸入端必須保持綁定在各自合適的高有效或低有效狀態。

邏輯功致,反輸。

CD74HC138 ,CD74HC238和CD74HCT138 , CD74HCT238是高速硅柵CMOS解碼器,適合內存地址解碼或數據路由應用。74HC138 作用原理於高性能的存貯解碼或要求傳輸延遲時間短的數據傳輸系統,在 高性能存貯器系統中,用這種解碼器可以提高解碼系統的效率。將快速賦能電路用於高速存貯器時,解碼器的延遲時間和存貯器的賦能時間通常小於存貯器的典型存取時間,這就是說由肖特基鉗位的系統解碼器所引起的有效系統延遲可以忽略不計。HC138 按照三位二進位輸入碼和賦能輸入條件,從8 個輸出端中譯出一個 低電平輸出。兩個低電平有效的賦能輸入端和一個高電平有效的賦能輸入端減少了擴展所需要的外接門或倒相器,擴展成24 線解碼器不需外接門;擴展成32 線解碼器,只需要接一個外接倒相器。在解調器應用中,賦能輸入端可用作數據輸入端。

74HC138集成解碼器功能表

複合使能輸入,輕鬆實現擴展 兼容JEDEC標準no.7A 存儲器晶元解碼選擇的理想選擇 低有效互斥輸出 ESD保護 HBM EIA/JESD22-A114-C超過2000 V MM EIA/JESD22-A115-A超過200 V 溫度範圍 -40~+85 ℃ -40~+125 ℃ 多路分配功能