PMOS管

一種晶體管

pmos PMOS是指n型襯底、p溝道,靠空穴的流動運送電流的MOS管,全稱為 positive channel Metal Oxide Semiconductor,別名為 positive MOS。

指型襯底、溝,靠空穴流運送流管。

稱:

別名: positive MOS

PMOS管

改變柵壓可以改變溝道中的電子密度,從而改變溝道的電阻。這種MOS場效應晶體管稱為P溝道增強型場效應晶體管。

如果N型硅襯底表面不加柵壓就已存在P型反型層溝道,加上適當的偏壓,可使溝道的電阻增大或減小。這樣的MOS場效應晶體管稱為P溝道耗盡型場效應晶體管。統稱為PMOS晶體管。

P溝道MOS晶體管的空穴遷移率低,因而在MOS晶體管的幾何尺寸和工作電壓絕對值相等的情況下,PMOS晶體管的跨導小於N溝道MOS晶體管。

此外,P溝道MOS晶體管閾值電壓的絕對值一般偏高,要求有較高的工作電壓。它的供電電源的電壓大小和極性,與雙極型晶體管——晶體管邏輯電路不兼容。

PMOS因邏輯擺幅大,充電放電過程長,加之器件跨導小,所以工作速度更低,在NMOS電路(見N溝道金屬—氧化物—半導體集成電路)出現之後,多數已為NMOS電路所取代。只是,因PMOS電路工藝簡單,價格便宜,有些中規模和小規模數字控制電路仍採用PMOS電路技術。

MOSFET共有三個腳,一般為G、D、S,通過G、S間加控制信號時可以改變D、S間的導通和截止。

PMOS和NMOS在結構上完全相像,所不同的是襯底和源漏的摻雜類型。簡單地說,NMOS是在P型硅的襯底上,通過選擇摻雜形成N型的摻雜區,作為NMOS的源漏區;PMOS是在N型硅的襯底上,通過選擇摻雜形成P型的摻雜區,作為PMOS的源漏區。

兩塊源漏摻雜區之間的距離稱為溝道長度L,而垂直於溝道長度的有效源漏區尺寸稱為溝道寬度W。對於這種簡單的結構,器件源漏是完全對稱的,只有在應用中根據源漏電流的流向才能最後確認具體的源和漏。

PMOS的工作原理與NMOS相類似。因為PMOS是N型硅襯底,其中的多數載流子是空穴,少數載流子是電子,源漏區的摻雜類型是P型,所以,PMOS的工作條件是在柵上相對於源極施加負電壓,亦即在PMOS的柵上施加的是負電荷電子,而在襯底感應的是可運動的正電荷空穴和帶固定正電荷的耗盡層,不考慮二氧化硅中存在的電荷的影響,襯底中感應的正電荷數量就等於PMOS柵上的負電荷的數量。

當達到強反型時,在相對於源端為負的漏源電壓的作用下,源端的正電荷空穴經過導通的P型溝道到達漏端,形成從源到漏的源漏電流。同樣地,VGS越負(絕對值越大),溝道的導通電阻越小,電流的數值越大。

與NMOS一樣,導通的PMOS的工作區域也分為非飽和區,臨界飽和點和飽和區。當然,不論NMOS還是PMOS,當未形成反型溝道時,都處於截止區,其電壓條件是

VGS

VGS>VTP (PMOS),

值得注意的是,PMOS的VGS和VTP都是負值。

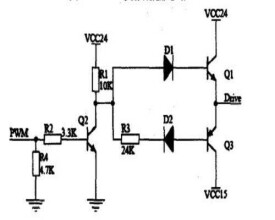

PMOS集成電路是一種適合在低速、低頻領域內應用的器件。PMOS集成電路採用-24V電壓供電。CMOS-PMOS介面電路採用兩種電源供電。採用直接介面方式,一般CMOS的電源電壓選擇在10~12V就能滿足PMOS對輸入電平的要求。

MOS場效應晶體管具有很高的輸入阻抗,在電路中便於直接耦合,容易製成規模大的集成電路。

各種場效應管特性比較

在2004年12月的國際電子器件會議(IEDM)上表示:雙應力襯墊(DSL)方法導致NMOS和PMOS中的有效驅動電流分別增加15%和32%,飽和驅動電流分別增加11%和20%。PMOS的空穴遷移率在不使用SiGe的情況下可以提高60%,這已經成為其他應變硅研究的焦點。

目錄