判決電路

判決電路

判決電路多見於電路結構中,其作用十分廣泛,有一定的選擇作用。

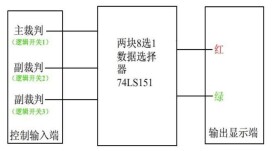

判決電路一種簡單的情況就是多數表決電路。比如判斷一個運動員的成績是否有效,可以設3個裁判,給出一定的判決條件,如:主裁判和至少一名副裁判判斷合格就合格。用數字電路實現。

判決電路多見於電路結構中,其作用十分廣泛,有一定的選擇作用。

列真值表;寫表達式;觀察後用語言文字描述功能;或者畫狀態圖;列狀態表;寫方程;觀察後用語言文字描述功能。

組合邏輯電路的功能多是:加法器、奇偶校驗器、減法器等等。

任何傳輸系統中都存在著通道失真、雜訊和干擾。通道失真是由有限的帶寬和色散等傳輸特性造成的,雜訊是由系統中電阻和有源器件的載流子的不規則起伏造成的,干擾則是由不可預測的外部因素造成的。由於受到通道失真、雜訊和干擾的影響,接收機接收到的信號就不可避免的出現失真和受到干擾,即使幅度衰減得到了補償,還常常是不能直接用作數據流。通道失真可在一定程度上利用均衡器來減小,而對雜訊和其他干擾的抑制就要依靠數據再生電路來實現。數據再生包括兩個子電路:時鐘恢復和數據判決電路。他們實際上是整個接收模塊的核心,其中的數據判決電路是光接收機的關鍵電路之一。

數據能夠恢復是基於它在時域內有明確的可描述的特徵。例如一個NRZ信號,在整個周期內保持高電平⋯1或者低電平“0”,當雜訊和其它干擾電壓相對於信號眼圖高低即高低電平之差很小時,信號為⋯0’電平或⋯1 電平就由取樣範圍內電平低於或高於閩值電平決定的。因此,數據可以通過與閾值電平進行比較作出正確的判決。當每一個確定的⋯0’信號和⋯1’信號用與發送端相同的信號波形再次表達后,數據序列將得到再生。由於數字傳輸系統中信號可以在通道中無差錯的多次再生,直到最後在接收機端無差錯或以極低的差錯率再生,這樣就大大提高了傳輸的距離和可靠性。

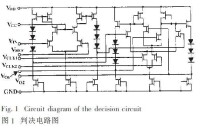

砷化鎵數字電路主要邏輯形式有: 緩衝FET 邏輯(BFL) 、肖特基二極體FET 邏輯( SDFL) 、直接耦合FET 邏輯(DCFL) 和源耦合FET 邏輯( SCFL) [ 3,4 ]。根據國內的材料與工藝條件,以及電路結構、速度、邏輯擺幅、功耗等多方面因素綜合考慮,通常採用SCFL 電路作為判決電路的基本單元電路。

判決電路