AD9850

AD9850

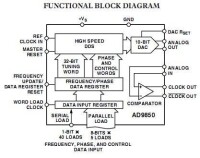

AD9850是AD公司生產的最高時鐘為125 MHz、採用先進的CMOS技術的直接頻率合成器,主要由可編程DDS系統、高性能數模變換器(DAC)和高速比較器3部分構成,能實現全數字編程式控制制的頻率合成。

原理框圖

相位寄存器每過 個外部參考時鐘后返回到初始狀態一次,相應地正弦查詢表

每經過一個循環也回到初始位置,從而使整個DDS 系統輸出一個正弦波。輸出的正弦波頻率,其中為外部參考時鐘頻率。

AD9850 採用32 位的相位累加器將信號截斷成14 位輸入到正弦查詢表,查詢表的輸出再被截斷成10 位后輸入到DAC ,DAC 再輸出兩個互補的電流。DAC 滿量程輸出電流通過一個外接電阻RSET調節,典型值3.9千歐。將DAC 的輸出經低通濾波後接到AD9850 內部的高速比較器上即可直接輸出方波。在125MHz 的時鐘下, 32 位頻率控制字可使AD9850 輸出頻率解析度達0. 0291Hz 。

AD9850有40 位控制字,32 位用於頻率控制(低32位),5 位用於相位控制,1 位用於電源休眠( Powerdown) 控制,2位用於選擇工作方式。這40 位控制字可通過并行或串列方式輸入到AD9850 。在并行裝入方式中,通過8 位匯流排D0 —D7將數據輸入到寄存器,在W - CL K 的上升沿裝入8位數據,並把指針指向下一個輸入寄存器,在重複5 次之後再在FQ - UD 上升沿把40位數據從輸入寄存器裝入到頻率/ 相位數據寄存器(更新DDS 輸出頻率和相位) ,同時把地址指針複位到第一個輸入寄存器。

AD9850的複位(RESET) 信號為高電平有效,且脈衝寬度不小於5 個參考時鐘周期。AD9850的參考時鐘頻率一般遠高於單片機的時鐘頻率(小廝所用為單片機89C51,使用12M晶振),因此AD9850 的複位(RESET)端可與單片機的複位端直接相連。