ATtiny2313

ATtiny2313

– 1 –

概念

ATtiny2313是基於增強的AVR RISC結構的低功耗8位CMOS微控制器。由於其先進的指令集以及單時鐘周期指令執行時間, ATtiny2313 的數據吞吐率高達1 MIPS/MHz,從而可以緩減系統在功耗和處理速度之間的矛盾。

AVR 內核

AVR 內核具有豐富的指令集和32 個通用工作寄存器。所有的寄存器都直接與算邏單元(ALU) 相連接,使得一條指令可以在一個時鐘周期內同時訪問兩個獨立的寄存器。這種結構大大提高了代碼效率,並且具有比普通的CISC 微控制器最高至10 倍的數據吞吐率。

ATtiny2313有2K位元組系統內可編程Flash,128位元組EEPROM,128位元組SRAM, 18 個通用 I/O 口線, 32 個通用工作寄存器,對片內調試的單線介面, 2 個具有比較模式的靈活的定時器/ 計數器,片內/ 外中斷,串列可編程USART,有啟動狀態檢測器的通用串列介面,含片內振蕩器的可編程看門狗定時器,以及三種可以通過軟體進行選擇的省電模式。工作於空閑模式時CPU 停止工作,而SRAM、T/C 以及中斷系統繼續工作;掉電模式時晶體振蕩器停止振蕩,所有功能除了中斷和硬體複位之外都停止工作; Standby 模式下只有晶體振蕩器運行,使得器件只消耗極少的電流,同時具有快速啟動能力。

本晶元是以Atmel 高密度非易失性存儲器技術生產的。通過SPI 串列介面或非易失性存儲器編程器可對程序存儲器進行系統內編程。通過將8 位RISC CPU 與系統內可編程的Flash 集成在一個晶元內,ATtiny2313 成為一個功能強大的單片機,為許多嵌入式控制應用提供了靈活而低成本的解決方案。

ATtiny2313 AVR 具有一整套的編程與系統開發工具,包括:C 語言編譯器、宏彙編、程序調試器/ 軟體仿器、模擬器及評估板。

· 使用 AVR® RISC 結構

· AVR – 高性能、低功耗的RISC 結構

– 120 條指令 – 大多數指令執行時間為單個時鐘周期

– 32 個8 位通用工作寄存器

– 全靜態工作

– 工作於20 MHz 時性能高達20 MIPS

· 數據與非易失性程序和數據存儲器

– 2K位元組的系統內可編程Flash

擦寫壽命: 10,000 次

– 128 位元組的系統內可編程EEPROM

擦寫壽命: 100,000 次

– 128 位元組的片內SRAM

– 可以對鎖定位進行編程以及實現EEPROM 數據的加密

· 外設特點

– 具有獨立預分頻器及比較模式的8 位定時器/ 計數器

– 具有獨立預分頻器及比較、捕獲模式的16 位定時器/ 計數器

– 四路 PWM 通道

– 片內模擬比較器

– 具有片內振蕩器的可編程看門狗定時器

– USI – 全局串列介面

– 全雙工 USART

· 特殊的處理器特點

– debugWIRE 片上調試

– 通過SPI 埠在系統內可編程

– 片內/ 片外中斷源

– 低功耗空閑模式、掉電模式、Standby 模式

– 增強型上電複位

– 可編程的掉電檢測

– 片內標定振蕩器

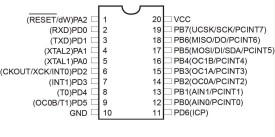

· I/O 和封裝

– 18可編程I/O 線

– 20引腳PDIP, 20 引腳 SOIC 與32 引腳MLF

· 工作電壓

– 1.8 - 5.5V (ATtiny2313V)

– 2.7 - 5.5V (ATtiny2313)

· 速度等級

– ATtiny2313V: 0 - 4 MHz @ 1.8 - 5.5V, 0 - 10 MHz @ 2.7 - 5.5V

– ATtiny2313: 0 - 10 MHz @ 2.7 - 5.5V, 0 - 20 MHz @ 4.5 - 5.5V

· 功耗估計

– 正常模式:

1 MHz, 1.8V: 300 μA

32 kHz, 1.8V: 20 μA ( 包括振蕩器)

– 掉電模式:

< 0.2 μA at 1.8V

VCC 數字電路的電源。

GND 地

埠A(pA2..PA0) 埠A 為3 位雙向I/O 口,具有可編程的內部上拉電阻。其輸出緩衝器具有對稱的驅動特性,可以輸出和吸收大電流。作為輸入使用時,若內部上拉電阻使能,埠被外部電路拉低時將輸出電流。在複位過程中,即使系統時鐘還未起振,埠A 處於高阻狀態。埠A 也可以用做其他不同的特殊功能。

埠B(PB7..PB0) 埠B 為8 位雙向I/O 口,具有可編程的內部上拉電阻。其輸出緩衝器具有對稱的驅動特性,可以輸出和吸收大電流。作為輸入使用時,若內部上拉電阻使能,埠被外部電路拉低時將輸出電流。在複位過程中,即使系統時鐘還未起振,埠B 處於高阻狀態。埠B 也可以用做其他不同的特殊功能。

埠D(PD6..PD0) 埠D 為7 位雙向I/O 口,具有可編程的內部上拉電阻。其輸出緩衝器具有對稱的驅動特性,可以輸出和吸收大電流。作為輸入使用時,若內部上拉電阻使能,埠被外部電路拉低時將輸出電流。在複位過程中,即使系統時鐘還未起振,埠D 處於高阻狀態。埠D 也可以用做其他不同的特殊功能。

的複位輸入。

XTAL1 反向振蕩放大器與片內時鐘操作電路的輸入端。 XTAL1 是 PA0 的第二功能。

XTAL2 反向振蕩放大器的輸出端。XTAL2 是 PA1 的第二功能。