SPI

一種高速的,全雙工,同步的通信匯流排

SPI是串列外設介面(Serial Peripheral Interface)的縮寫,是一種高速的,全雙工,同步的通信匯流排,並且在晶元的管腳上只佔用四根線,節約了晶元的管腳,同時為PCB的布局上節省空間,提供方便,正是出於這種簡單易用的特性,越來越多的晶元集成了這種通信協議,比如AT91RM9200。

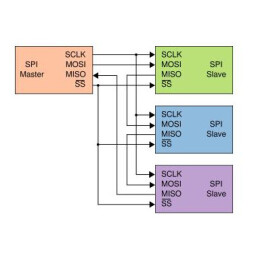

SPI匯流排是一種4線匯流排,因其硬體功能很強,所以與SPI有關的軟體就相當簡單,使中央處理器(Central Processing Unit,CPU)有更多的時間處理其他事務。正是因為這種簡單易用的特性,越來越多的晶元集成了這種通信協議,比如AT91RM9200。SPI是一種高速、高效率的串列介面技術。通常由一個主模塊和一個或多個從模塊組成,主模塊選擇一個從模塊進行同步通信,從而完成數據的交換。SPI是一個環形結構,通信時需要至少4根線(事實上在單向傳輸時3根線也可以)。

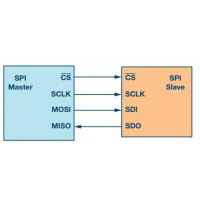

SPI的通信原理很簡單,它以主從方式工作,這種模式通常有一個主設備和一個或多個從設備,需要至少4根線,事實上3根也可以(單向傳輸時)。也是所有基於SPI的設備共有的,它們是MISO(主設備數據輸入)、MOSI(主設備數據輸出)、SCLK(時鐘)、CS(片選)。

(1)MISO–Master Input Slave Output,主設備數據輸入,從設備數據輸出;

(2)MOSI–Master Output Slave Input,主設備數據輸出,從設備數據輸入;

(3)SCLK–Serial Clock,時鐘信號,由主設備產生;

(4)CS–Chip Select,從設備使能信號,由主設備控制。

其中,CS是從晶元是否被主晶元選中的控制信號,也就是說只有片選信號為預先規定的使能信號時(高電位或低電位),主晶元對此從晶元的操作才有效。這就使在同一條匯流排上連接多個SPI設備成為可能。

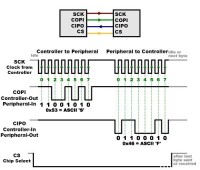

接下來就負責通訊的3根線了。通訊是通過數據交換完成的,這裡先要知道SPI是串列通訊協議,也就是說數據是一位一位的傳輸的。這就是SCLK時鐘線存在的原因,由SCLK提供時鐘脈衝,SDI,SDO則基於此脈衝完成數據傳輸。數據輸出通過SDO線,數據在時鐘上升沿或下降沿時改變,在緊接著的下降沿或上升沿被讀取。完成一位數據傳輸,輸入也使用同樣原理。因此,至少需要8次時鐘信號的改變(上沿和下沿為一次),才能完成8位數據的傳輸。

時鐘信號線SCLK只能由主設備控制,從設備不能控制。同樣,在一個基於SPI的設備中,至少有一個主設備。這樣的傳輸方式有一個優點,在數據位的傳輸過程中可以暫停,也就是時鐘的周期可以為不等寬,因為時鐘線由主設備控制,當沒有時鐘跳變時,從設備不採集或傳送數據。SPI還是一個數據交換協議:因為SPI的數據輸入和輸出線獨立,所以允許同時完成數據的輸入和輸出。晶元集成的SPI串列同步時鐘極性和相位可以通過寄存器配置,IO模擬的SPI串列同步時鐘需要根據從設備支持的時鐘極性和相位來通訊。

最後,SPI介面的一個缺點:沒有指定的流控制,沒有應答機制確認是否接收到數據。

SPI的片選可以擴充選擇16個外設,這時PCS輸出=NPCS,說NPCS0~3接4-16解碼器,這個解碼器是需要外接4-16解碼器,解碼器的輸入為NPCS0~3,輸出用於16個外設的選擇。

SPI是一個環形匯流排結構,由ss(cs)、sck、sdi、sdo構成,主要是在sck的控制下,兩個雙向移位寄存器進行數據交換。

假設下面的8位寄存器裝的是待發送的數據10101010,上升沿發送、下降沿接收、高位先發送。

那麼第一個上升沿來的時候數據將會是sdo=1;寄存器=0101010x。下降沿到來的時候,sdi上的電平將鎖存到寄存器中去,那麼這時寄存器=0101010sdi,這樣在8個時鐘脈衝以後,兩個寄存器的內容互相交換一次。這樣就完成了一個spi時序。

舉例:假設主機和從機初始化就緒:並且主機的sbuff(串列口收發緩衝器)=0xaa,從機的sbuff(串列口收發緩衝器)=0x55,下面將分步對spi的8個時鐘周期的數據情況演示一遍:

這樣就完成了兩個寄存器8位的交換,上面的上表示上升沿、下表示下降沿,sdi、sdo相對於主機而言的。其中ss引腳作為主機的時候,從機可以把它拉低被動選為從機,作為從機的時候,可以作為片選腳用。根據以上分析,一個完整的傳送周期是16位,即兩個位元組,因為,首先主機要發送命令過去,然後從機根據主機的命令準備數據,主機在下一個8位時鐘周期才把數據讀回來。

SPI匯流排是Motorola公司推出的三線同步介面,同步串列3線方式進行通信:一條時鐘線SCK,一條數據輸出線MOSI,一條數據輸入線MISO;用於CPU與各種外圍器件進行全雙工、同步串列通訊。SPI主要特點有:可以同時發出和接收串列數據;可以當作主機或從機工作;提供頻率可編程時鐘;發送結束中斷標誌;寫衝突保護;匯流排競爭保護等。下圖示出SPI匯流排工作的四種方式,其中使用的最為廣泛的是SPI0和SPI3方式(實線表示):

SPI

該模塊針對用戶不同的應用來設計,本質上就是用戶的具體業務應用,與SPI-4介面沒有直接關係。當應用支持多個埠時,這部分就顯得至關重要。下面以支持兩個埠的應用來說明用戶邏輯的設計技巧。

(1)Sink Core的用戶邏輯

埠為兩個時,用戶邏輯就需要用兩個不同的FIFO根據埠的地址等來分別緩存用戶的兩個業務數據,同時根據FIFO的情況來發出流控信息給SPI4數據介面。

SPI

(2)Source Core的用戶邏輯

當埠為兩個時,用戶邏輯就需要根據流控信息和兩個不同的FffiOffJ情況來做仲裁,諛定哪個用戶邏輯FIFO需要發送給SPI4數據介面。

SPI有3種規格。

3種SPI的處理流程大同小異,使用最多的SPI-4為例來說明SPI的原理。它在發送介面和接收介面都有各自的數據通道和流控狀態信息通道,其數據通道和流控狀態信息通道是獨立的並且是點對點通信。數據是以包的形式發送,根據數據包中的內嵌地址可支持高達256個埠,以下分別說明基本協議及數據通道和流控狀態信息的處理過程。

SPI時序圖詳解---SPI介面在模式0下輸出第一位數據的時刻。

SPI

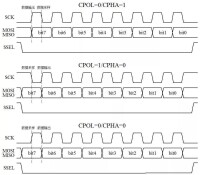

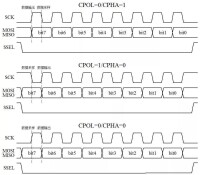

SPI介面有四種不同的數據傳輸時序,取決於CPOL和CPHL這兩位的組合。圖1中表現了這四種時序,時序與CPOL、CPHA的關係也可以從圖中看出。

CPOL是用來決定SCK時鐘信號空閑時的電平,CPOL=0,空閑電平為低電平,CPOL=1時,空閑電平為高電平。CPHA是用來決定採樣時刻的,CPHA=0,在每個周期的第一個時鐘沿採樣,CPHA=1,在每個周期的第二個時鐘沿採樣。

SPI:高速同步串列口。是一種標準的四線同步雙向串列匯流排。

SPI,是英語Serial Peripheral interface的縮寫,顧名思義就是串列外圍設備介面。是Motorola首先在其MC68HCXX系列處理器上定義的。SPI介面主要應用在EEPROM,FLASH,實時時鐘,AD轉換器,還有數字信號處理器和數字信號解碼器之間。

SPI匯流排系統是一種同步串列外設介面,它可以使MCU與各種外圍設備以串列方式進行通信以交換信息。外圍設置FLASHRAM、網路控制器、LCD顯示驅動器、A/D轉換器和MCU等。SPI匯流排系統可直接與各個廠家生產的多種標準外圍器件直接介面,該介面一般使用4條線:串列時鐘線(SCLK)、主機輸入/從機輸出數據線MISO、主機輸出/從機輸入數據線MOSI和低電平有效的從機選擇線SS(有的SPI介面晶元帶有中斷信號線INT、有的SPI介面晶元沒有主機輸出/從機輸入數據線MOSI)。

SPI的通信原理很簡單,它以主從方式工作,這種模式通常有一個主設備和一個或多個從設備,需要至少4根線,事實上3根也可以(用於單向傳輸時,也就是半雙工方式)。也是所有基於SPI的設備共有的,它們是SDI(數據輸入)、SDO(數據輸出)、SCLK(時鐘)、CS(片選)。

(1)MOSI–SPI匯流排主機輸出/從機輸入(SPI Bus Master Output/Slave Input);

(2)MISO–SPI匯流排主機輸入/從機輸出(SPI Bus Master Input/Slave Output);

(3)SCLK–時鐘信號,由主設備產生;

(4)CS–從設備使能信號,由主設備控制(Chip select),有的IC此pin腳叫SS。

其中CS是控制晶元是否被選中的,也就是說只有片選信號為預先規定的使能信號時(高電位或低電位),對此晶元的操作才有效。這就允許在同一匯流排上連接多個SPI設備成為可能。

接下來就負責通訊的3根線了。通訊是通過數據交換完成的,這裡先要知道SPI是串列通訊協議,也就是說數據是一位一位的傳輸的。這就是SCLK時鐘線存在的原因,由SCK提供時鐘脈衝,SDI,SDO則基於此脈衝完成數據傳輸。數據輸出通過SDO線,數據在時鐘上升沿或下降沿時改變,在緊接著的下降沿或上升沿被讀取。完成一位數據傳輸,輸入也使用同樣原理。這樣,在至少8次時鐘信號的改變(上沿和下沿為一次),就可以完成8位數據的傳輸。

在點對點的通信中,SPI介面不需要進行定址操作,且為全雙工通信,顯得簡單高效。在多個從設備的系統中,每個從設備需要獨立的使能信號,硬體上比I2C系統要稍微複雜一些。

在多個從器件的系統中,每個從器件需要獨立的使能信號,硬體上比I2C系統要稍微複雜一些。

SPI介面在內部硬體實際上是兩個簡單的移位寄存器,傳輸的數據為8位,在主器件產生的從器件使能信號和移位脈衝下,按位傳輸,高位在前,低位在後。如下圖所示,在SCLK的下降沿上數據改變,同時一位數據被存入移位寄存器。

AT91RM9200的SPI介面主要由4個引腳構成:SPICLK、MOSI、MISO及 NSS,其中SPICLK是整個SPI匯流排的公用時鐘,MOSI、MISO作為主機,從機的輸入輸出的標誌,MOSI是主機的輸出,從機的輸入,MISO是主機的輸入,從機的輸出。NSS是從機的標誌管腳,在互相通信的兩個SPI匯流排的器件,NSS管腳的電平低的是從機,相反NSS管腳的電平高的是主機。在一個SPI通信系統中,必須有主機。SPI匯流排可以配置成單主單從,單主多從,互為主從。

SPI的片選可以擴充選擇16個外設,這時PCS輸出=NPCS,說NPCS0~3接4-16解碼器,這個解碼器是需要外接4-16解碼器,解碼器的輸入為NPCS0~3,輸出用於16個外設的選擇。

SPI介面的一個缺點:沒有指定的流控制,沒有應答機制確認是否接收到數據。

上文中最後一句話:SPI主模塊和與之通信的外設備時鐘相位和極性應該一致。個人理解這句話有2層意思:其一,主設備SPI時鐘和極性的配置應該由外設來決定;其二,二者的配置應該保持一致,即主設備的SDO同從設備的SDO配置一致,主設備的SDI同從設備的SDI配置一致。因為主從設備是在SCLK的控制下,同時發送和接收數據,並通過2個雙向移位寄存器來交換數據。工作原理演示如下圖:

上升沿主機SDO發送數據1,同時從設備SDO發送數據0;緊接著在SCLK的下降沿的時候從設備的SDI接收到了主機發送過來的數據1,同時主機也接收到了從設備發送過來的數據0。

SPI介面時鐘配置心得:在主設備這邊配置SPI介面時鐘的時候一定要弄清楚從設備的時鐘要求,因為主設備這邊的時鐘極性和相位都是以從設備為基準的。因此在時鐘極性的配置上一定要搞清楚從設備是在時鐘的上升沿還是下降沿接收數據,是在時鐘的下降沿還是上升沿輸出數據。但要注意的是,由於主設備的SDO連接從設備的SDI,從設備的SDO連接主設備的SDI,從設備SDI接收的數據是主設備的SDO發送過來的,主設備SDI接收的數據是從設備SDO發送過來的,所以主設備這邊SPI時鐘極性的配置(即SDO的配置)跟從設備的SDI接收數據的極性是相反的,跟從設備SDO發送數據的極性是相同的。下面這段話是Sychip Wlan8100 Module Spec上說的,充分說明了時鐘極性是如何配置的:

The 81xx module will always input data bits at the rising edge of the clock,and the host will always output data bits on the falling edge of the clock.

意思是:主設備在時鐘的下降沿發送數據,從設備在時鐘的上升沿接收數據。因此主設備這邊SPI時鐘極性應該配置為下降沿有效。

又如,下面這段話是摘自LCD Driver IC SSD1289:

SDI is shifted into 8-bit shift register on every rising edge of SCK in the order of data bit 7,data bit 6 …… data bit 0。

意思是:從設備SSD1289在時鐘的上升沿接收數據,而且是按照從高位到低位的順序接收數據的。因此主設備的SPI時鐘極性同樣應該配置為下降沿有效。

時鐘極性和相位配置正確后,數據才能夠被準確的發送和接收。因此應該對照從設備的SPI介面時序或者Spec文檔說明來正確配置主設備的時鐘。

假設主機和從機初始化就緒:並且主機的sbuff=0xaa,從機的sbuff=0x55,下面將分步對spi的8個時鐘周期的數據情況演示一遍:假設上升沿發送數據

脈衝主機sbuff從機sbuff sdi sdo

0 10101010 01010101 0 0

1上 0101010x 1010101x 0 1

1下 01010100 10101011 0 1

2上 1010100x 0101011x 1 0

2下 10101001 01010110 1 0

3上 0101001x 1010110x 0 1

3下 01010010 10101101 0 1

4上 1010010x 0101101x 1 0

4下 10100101 01011010 1 0

5上 0100101x 1011010x 0 1

5下 01001010 10110101 0 1

6上 1001010x 0110101x 1 0

6下 10010101 01101010 1 0

7上 0010101x 1101010x 0 1

7下 00101010 11010101 0 1

8上 0101010x 1010101x 1 0

8下 01010101 10101010 1 0

這樣就完成了兩個寄存器8位的交換,上面的上表示上升沿、下表示下降沿,sdi、sdo相對於主機而言的。其中ss引腳作為主機的時候,從機可以把它拉底被動選為從機,作為從機的是時候,可以作為片選腳用。根據以上分析,一個完整的傳送周期是16位,即兩個位元組,因為,首先主機要發送命令過去,然後從機根據主機的命令準備數據,主機在下一個8位時鐘周期才把數據讀回來。SPI匯流排是Motorola公司推出的三線同步介面,同步串列3線方式進行通信:一條時鐘線SCK,一條數據輸入線MISO,一條數據輸出線MOSI;用於CPU與各種外圍器件進行全雙工、同步串列通訊。SPI主要特點有:可以同時發出和接收串列數據;可以當作主機或從機工作;提供頻率可編程時鐘;發送結束中斷標誌;寫衝突保護;匯流排競爭保護等。下圖示出SPI匯流排工作的四種方式,其中使用的最為廣泛的是SPI0和SPI3方式(實線表示):

SPI匯流排四種工作方式SPI模塊為了和外設進行數據交換,根據外設工作要求,其輸出串列同步時鐘極性和相位可以進行配置,時鐘極性(CPOL)對傳輸協議沒有重大的影響。如果CPOL=0,串列同步時鐘的空閑狀態為低電平;如果CPOL=1,串列同步時鐘的空閑狀態為高電平。時鐘相位(CPHA)能夠配置用於選擇兩種不同的傳輸協議之一進行數據傳輸。如果CPHA=0,在串列同步時鐘的第一個跳變沿(上升或下降)數據被採樣;如果CPHA=1,在串列同步時鐘的第二個跳變沿(上升或下降)數據被採樣。SPI主模塊和與之通信的外設備時鐘相位和極性應該一致。

SPI(schedule performance index)=BCWP/BCWS

其中,BCWP--已完成工作預算費用(掙值)=已完工程量×預算單價;BCWS--計劃完成工作預算費用=計劃工程量×預算單價;SPI>1說明進度超前,符合要求;SPI<1說明進度延遲,應採取措施糾正!

Sales Performance International(SPI)是解決方案銷售(Solution Selling®)方法的知識產權所有者——全球備受承認的銷售培訓可為銷售人員和管理專業人士提供成熟、完整、端到端的專業發展計劃。

SPI亞洲總部位於新加坡,通過與顧客精誠合作,在亞洲地區開展了廣泛而深入的工作,通過提供戰略、運營及戰術層次上的解決方案來幫助客戶提升銷售業績。SPI成立於1988年,已幫助多家公司成功地從銷售產品轉變為營銷和銷售高價值的解決方案,是業內的領導者。SPI已在50個以上的國家內使用14種以上的語言為超過60萬名的銷售及管理專業人士提供過培訓,具備足夠的專業技能來為客戶提供合適的解決方案,可幫助客戶實現可衡量及可持續的收入增長和可執行的銷售業績提升。

SPI,母豬繁殖指數(Swine Productivity Index),也叫繁殖經濟效益指數。

SPI:Software Process Improvement.軟體過程改進。是軟體企業項目過程質量的改進,CMM,ISO9000-3說的就是這個。

SPI:SDH Physical Interface.SDH物理介面。SPI是設備和光路的介面,主要完成光/電變換,電/光變換,提取線路定時,以及相應告警的檢測。

在SMT行業中指的是錫膏檢測設備(Solder Paste Inspection)的英文簡稱,用於錫膏印刷后檢測錫膏的高度、體積、面積、短路和偏移量。

SPI公司是著名的兵棋設計人鄧尼根在離開阿瓦隆山公司后開辦的兵棋設計公司,旗下有多部雜誌和著名兵棋。為“第三世界設計”和阿瓦隆山公司成美國兵棋界三巨頭之勢。后被設計《龍與地下城》的桌游公司收購,往日威力減弱了很多。

SPI,samples per inch,表示每英寸中所含的分離像素點的個數。

掃描儀為了獲得最佳效果,需要根據輸出設備(激光印表機、平板印刷機、直接數碼印刷)對它的SPI進行調整。通常確定掃描照片spi的公式是由網線版(halftone screen)或印表機嘗試使用的網線頻率(screen ruling)來決定。

標準化降水指數SPI(Standardized Precipitation Index):由於不同時間、不同地區降水量變化幅度很大,直接用降水量很難在不同時空尺度上相互比較,而且降水分佈是一種偏態分佈,不是正態分佈,所以在降水分析中,採用r分佈概率來描述降水量的變化,然後再經正態標準化求得SPI值。

乾旱指標的發展經歷了由最初只是反映降水多少的簡單指標到如今建立針對某一具體問題的複雜模型(如PDSI、KBDI)。中國科學工作者在乾旱指標的制定和應用方面作了大量工作,但是由於乾旱的複雜性和影響的廣泛性,迄今為止還沒有建立起完善統一的乾旱指標體系,不同地區、不同領域使用不同尺度的乾旱指標,這樣大大降低了乾旱等級的可比性和乾旱監測的連續性。SPI可以計算不同時間尺度的指標值,滿足多種水分監測需求,可以為不同部門和領域提供一個統一的乾旱指標。

SPI同z指數一樣存在因不涉及乾旱機理而產生的不足。首先,由於SPI的計算特性,不同地點的乾旱等級頻度相同,即假定了所有地點發生旱澇極端事件的概率相同,無法標識旱澇頻發地區。其次,除由於降水偏少影響以外,氣候變暖蒸發加大也是造成乾旱的重要因素(方修琦等,1997),而SPI沒有考慮氣溫、蒸發對乾旱的影響。最後,SPI值的計算是建立在長nCfnq序列基礎上的,其單月值是在該時間序列同一時期平均水平上的反映。與濕季同樣多的甚至是少的降水量在旱季的sPI值會大得多。

參考值:正常情況:SPI<0.1表示選擇性好 SPI0.1~0.2表示選擇性一般 SPI>0.2表示選擇性差。

臨床意義:當尿中排出大分子IgG的量少時,表示選擇性好。相反,表示選擇性差。

一、SPI 是英文Software Process Improvement的縮寫,中文意思是軟體過程的改進。它是CMM(還有其他能力模型)中的一個重要概念,CMM模型的目的就是要改進一個組織的過程,提高過程能力,所以叫做SPI-軟體過程改進。

二、SPI 是英文Service Provider Interface的縮寫。中文意思是服務提供商介面。滿足某種服務標準的供應商提供的符合該標準的應用程序介面,SPI應該和該服務的API標準是兼容的,應用程序一般應該是基於API編寫,除非是SPI中包含API中沒有提供的功能而又必須使用。

三、SPI:Standardized Precipitation Index 標準化降水指數,是一種用伽馬分佈來擬合降雨量然後將積累概率等概率轉換成標準正態分佈對應值的一種乾旱指數。

四、SPI 是英文Single Program Initiation的縮寫。中文意思是單個程序啟動。

五、SPI:Security Parameter Index,安全參數索引。IPSec協議基本概念之一。是一個32比特的數值,在每一個IPSec報文中都攜帶該值。SPI、IP目的地址、安全協議號三者結合起來共同構成一個三元組,來標識一個特定的安全聯盟(Security Association)。

六、SPI理論:心理學中在記憶部分,SPI是SERIAL(記憶系統的編碼是串列的),PARALLEL(存儲是并行的),INDEPENDENT(提取是獨立的)的縮寫。在1995年,由Tulving提出,試圖將記憶系統和記憶過程的概念統一到一個更綜合的框架中。

七、SPI----Standard Process Instruction標準作業指導。

八、SPI The Society of the Plastics Industry,Inc 美國塑料工業協會。

九、SPI Soybean Protein Isolate,大豆分離蛋白。

十、SPI:stitch per inch 針/英寸,服裝專業用語。

十一、SPI:進度績效指數,掙值與計劃價值之比,反應了項目團隊利用時間的效率