二進位計數器

二進位計數器

計數器的種類很多。按時鐘脈衝輸入方式的不同,可分為同步計數器和非同步計數器;按進位體制的不同,可分為二進位計數器和非二進位計數器;按計數過程中數字增減趨勢的不同,可分為加計數器、減計數器和可逆計數器。

二進位非同步加計數器

二進位的轉換

電路結構

以三位二進位非同步加法計數器為例,如圖8.4.1所示。該電路由3個上升沿觸發的D觸發器組成,具有以下特點:每個D觸發器輸入端接該觸發器Q 端信號,因而Q n+1=Q n,即各D觸發器均處於計數狀態;計數脈衝加到最低位觸發器的C端,每個觸發器的Q 端信號接到相鄰高位的C端。

(2)原理分析:

假設各觸發器均處於0態,根據電路結構特點以及D觸發器工作特性,不難得到其狀態圖和時序圖,它們分別如圖8.4.2和圖8.4.3所示。其中虛線是考慮觸發器的傳輸延遲時間TPD后的波形。

由狀態圖可以清楚地看到,從初始狀態000(由清零脈衝所置)開始,每輸入一個計數脈衝,計數器的狀態按二進位遞增(加1),輸入第8個計數脈衝后,計數器又回到000狀態。因此它是23進位加計數器,也稱模八(M=8)加計數器。

從時序圖可以清楚地看到Q0,Q1,Q2的周期分別是計數脈衝(CP)周期的2倍,4倍、8倍,也就是說Q0,Q1,Q2,分別對CP波形進行了二分頻,四分頻,八分頻,因而計數器也可作為分頻器。

需要說明的是,由圖8.4.3中的虛線波形可知,在考慮各觸發器的傳輸延遲時間tpd時,對於一個n 位的二進位非同步計數器來說,從一個計數脈衝(設為上升沿起作用)到來,到n 個觸發器都翻轉穩定,需要經歷的最長時間是ntpd ,為保證計數器的狀態能正確反應計數脈衝的個數,下一個計數脈衝(上升沿)必須在ntpd 後到來,因此計數脈衝的最小周期Tmin=ntpd 。

二進位非同步減計數器

圖8.4.4是3位二進位非同步減計數器的邏輯圖和狀態圖。從初態000開始,在第一個計數脈衝作用后,觸發器FF0由0翻轉為1(Q0的借位信號),此上升沿使FF1也由0翻轉為1(Q1的借位信號),這個上升沿又使FF2 由0翻轉為1,即計數器由000變成了111狀態。在這一過程中,Q0向Q1進行了借位,Q1向Q2進行了借位。此後,每輸入1個計數脈衝,計數器的狀態按二進位遞減(減1)。輸入第8個計數脈衝后,計數器又回到000狀態,完成一次循環。因此,該計數器是23進位(模8)非同步減計數器,它同樣具有分頻作用。

綜上所述,可對二進位非同步計數器歸納出以下兩點:

(1)n位二進位非同步計數器由n個處於計數工作狀態(對於D 觸發器,使Di=Qin;對於JK 觸發器,使Ji=Ki=1) 的觸發器組成。各觸發器之間的連接方式由加、減計數方式及觸發器的觸發方式決定。對於加計數器,若用上升沿觸發的觸發器組成,則應將低位觸發器的Q 端與相鄰高一位觸發器的時鐘脈衝輸入端相連(即進位信號應從觸發器的Q 端引出);若用下降沿觸發的觸發器組成,則應將低位觸發器的Q 端與相鄰高一位觸發器的時鐘脈衝輸入端連接。對於減計數器,各觸發器的連接方式則相反。

(2)在二進位非同步計數器中,高位觸發器的狀態翻轉必須在低一位觸發器產生進位信號(加計數)或借位信號(減計數)之後才能實現。故又稱這種類型的計數器為串列計數器。也正因為如此,非同步計數器的工作速度較低。

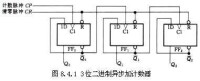

二進位同步計數器

為了提高計數速度,可採用同步計數器,其特點是,計數脈衝同時接於各位觸發器的時鐘脈衝輸入端,當計數脈衝到來時,各觸發器同時被觸發,應該翻轉的觸發器是同時翻轉的,沒有各級延遲時間的積累問題。同步計數器也可稱為并行計數器。

1.二進位同步加計數器

圖8.4.5是用JK觸發器(但已令J=K)組成的4位二進位(M=16)同步加計數器。

由圖可見,各位觸發器的時鐘脈衝輸入端接同一計數脈衝CP ,各觸發器的驅動方程分別為J0=K0=1,J1=K1=Q0、J2=K2=Q0Q1、 J3=K3=Q0Q1Q2 。

根據同步時序電路的分析方法,可得到該電路的狀態表,如表8.4.1所示。設從初態0000開始,因為J0=K0=1,所以每輸入一個計數脈衝CP,最低位觸發器FF0就翻轉一次,其他位的觸發器FFi僅在 Ji=Ki=Qi-1Qi-2……Q0=1的條件下,在CP 下降沿到來時才翻轉。

圖8.4.6是圖8.4.5電路的時序圖,其中虛線是考慮觸發器的傳輸延遲時間tpd 后的波形。由此圖可知,在同步計數器中,由於計數脈衝CP 同時作用於各個觸發器,所有觸發器的翻轉是同時進行的,都比計數脈衝CP 的作用時間滯后一個tpd ,因此其工作速度一般要比非同步計數器高。

應當指出的是,同步計數器的電路結構較非同步計數器複雜,需要增加一些輸入控制電路,因而其工作速度也要受這些控制電路的傳輸延遲時間的限制。如果將圖8.4.5電路中觸發器FF1、FF2和FF3的驅動信號分別改為即可構成4位二進位同步減計數器。

二進位同步可逆計數器

實際應用中,有時要求一個計數器即能作加計數又能作減計數。同時兼有加和減兩種計數功能的計數器稱為可逆計數器。

4位二進位同步可逆計數器如圖8.4.7所示,它是在前面介紹的4位二進位同步加和減計數器的基礎上,增加一控制電路構成的。由圖可知,各觸發器的驅動方程分別為當加/減控制信號X=1時,FF1-FF3中的各J、K 端分別與低位各觸發器的Q 端接通,進行加計數;當X=0時,各J、K 端分別與低位各觸發器的Q 端接通,進行減計數,實現了可逆計數器的功能。