亞微米和深亞微米MOS器件

亞微米和深亞微米MOS器件

亞微米和深亞微米MOS器件,通常把0.8-0.35um稱為亞微米,屬電子工程器件。

通常把0.8-0.35um稱為亞微米,0.25um及其以下稱為深亞微米,0.05um及其以下稱為納米級。深亞微米製造的關鍵技術主要包括紫外光刻技術、等離子體刻蝕技術、離子注入技術、同互連技術等。目前,國際上集成電路的主流生產工藝技術為0.18-0.25um,預計2006年主流加工技術將提高到0.lum,2012年將達到0.05um,進入納米級。深亞微米集成電路要求硅單晶材料向大直徑和無(少)缺陷方向發展。對於已開始應用的300毫米硅單晶而言,磁場拉晶、計算機模擬、線切割、雙面拋光等工藝成為大直徑硅單晶研製的重要特徵;利用晶體生長速率和固液界面的溫度梯度的設計,硅單晶中的自間隙硅原子、空位以及相關的微缺陷可以被控制;通過快速熱處理,引入和控制空位,進而控制氧沉澱的新型內吸雜技術,可以製備高質量的表面清潔區;利用氮雜質摻雜,可以抑制硅單晶中VOID缺陷和增加矽片的機械強度. 超深亞微米集成電路和微機電系統的膜/基和多層異質膜結構及內導線結構所用材料尺度逐漸由微米級減小到亞微米甚至納米級,即處於傳統宏觀與微觀範疇之間的介觀材料領域,其服役可靠性問題具有持久的挑戰性。材料性能的尺度效應,表面和界面效應及異質約束效應等愈加凸現,成為影響其可靠性的決定性因素之一。因此,材料介觀性能,特別是服役性能的正確表徵成為關係到提高微器件設計製造水平和服役可靠性而亟待解決的關鍵問題.

當前硅集成電路工業已進入0.5μm特徵尺寸產品的大生產階段,0.35μm工藝也已投入試生產。1994年半導體工業協會公布了1995—2010年15年間集成電路技術發展的預測。21世紀頭10年將面臨如何進行0.1μm級電路的設計和製造問題。生產工藝從微米、亞微米發展到深亞微米,這一變化對集成電路設計及其設計方法學 提出了新的問題和挑戰。首先要解決的是建立起精確的深亞微米器件模型、時序模型和互連模型。在深亞微米級電路設計中的一個突出矛盾是時序問題。到了深亞微米水平,互連線的延遲將超過門延遲;而且由於集成電路工作頻率的提高,允許的時序容差變小,傳輸延遲的影響加大,這對電路設計帶來了難度。在微米級電路設計時,習慣上把設計分成前後兩個階段。前一階段統稱邏輯設計,這時進行系統和功能設計以及結構和電路設計;后一階段稱為版圖設計,主要進行布局、布線以及物理驗證和掩膜生成。兩者之間的溝通主要通過網表和單元庫。前端設計完成後將網表傳遞給版圖設計人員,一般講只要布線能夠布通,時序要求就能夠滿足。到了深亞微米階段,情況就不同了,如果前端設計中不能充分考慮後端設計即物理實現時的各種問題,特別是物理實現后引起的時序問題,那就會造成邏輯設計與物理設計的結果不一致。在邏輯設計中經過模擬分析在功能和時序上都正確的網表,經過實際的布局布線后,由於互連延遲取決於具體的布線且在整個晶元延遲中起主要作用,更由於邏輯設計時所用的互連延遲模型與實際的互連延遲特性不一致,因而最終的時序會變得不再滿足設計要求。這就需要反過來修改邏輯設計,重新進行模擬分析。如果邏輯設計仍不能取得精確的、實際的互連延遲數據,那麼即使經過修改仍不能得到合乎要求的物理設計。如此下去,就會導致邏輯設計與物理設計的設計循環“不收斂”,使設計周期大大加長。

隨著集成電路製造工藝水平進入集成電路線寬的深亞微米時代,集成電路中的MOS元件都採用LDD結構(Lightly Doped Drain),並且硅化物工藝已廣泛應用於MOS元件的擴散層上,同時為了降低柵極多晶的擴散串聯電阻,採用了多晶化合物的製造工藝。此外隨著集成電路元件的縮小,MOS元件的柵極氧化層厚度越來越薄,這些製造工藝的改進可大幅度提高集成電路內部的運算速度,並可提高電路的集成度。但是這些工藝的改進帶來了一個很大的弊端,即深亞微米集成電路更容易遭受到靜電衝擊而失效,從而造成產品的可靠性下降。

(1)工藝引入問題

LDD結構是用來降低MOS管源端和漏端在溝道的電場分佈,以克服熱載流子效應(Hot carriereffect)所造成的I-V特性因長時間作用而漂移的問題。但是LDD結構在導電溝道兩段的深度只有20nm,這等於在源極和漏極的兩端形成了兩個"尖端","尖端放電"現象便容易發生在LDD結構上,從而造成這種結構的抗靜電能力較低。當這種LDD元件應用於輸出級電路時,NMOS元件很容易被ESD所破壞。即使元件具有很大的寬長比,其抗靜電能力常低於1 000V。此外,金屬硅化物工藝在深亞微米集成電路工藝中已被廣泛採用,其目的是為了降低MOS元件在其源極和漏極的串聯電阻。在不採用金屬硅化物工藝的條件下,N+擴散區的阻值約為30~40Ω/□,但在金屬硅化物工藝條件下其阻值降低到1~3Ω/□,由於擴散層的方塊電阻大幅降低,使得MOS元件的速度可以大幅度提高。但當金屬硅化物擴區的MOS元件被用來做輸出級的元件時,由於其源漏電阻都很小,ESD電流便很容易經由PAD傳導到MOS元件的LDD結構,極容易因LDD"尖端放電"而把MOS元件破壞掉,故在深亞微米集成電路中,MOS元件的ESD能力大幅度下滑,製造大尺寸的輸出級元件也無法有效地提升其抗靜電能力。

(2)傳統電路ESD保護設計及其缺陷

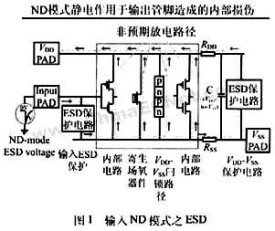

在傳統ESD設計上,靜電保護元件一般只做在I/O與VSS之間,在PAD與VDD、VSS和VDD之間沒有靜電保護元件,在這種靜電保護設計之下,集成電路內部常出現異常損傷問題。在對地正脈衝(PS)、對地負脈衝(NS)、對電源正脈衝(PD)、對電源負脈衝(ND)四种放電模式中,在圖1中ND模式的靜電放電負電壓出現在輸入與VDD之間,VDD在此模式下接地,此負的ESD電壓會首先經由輸入保護電路傳遞到VSS電源線上,因VSS電源線在此模式下是浮接的,故加在輸入上的負電壓會被傳遞到VSS上,在此模式下,原本電壓降在輸入與VDD之間的負ESD電壓,轉變成降在VDD與VSS之間,如果該ESD電壓未能有效且快速的被VDD到VSS的靜電放電保護電路旁路掉,ESD電壓會由VDD與VSS電源線而進入集成電路內部。由於內部元件具有最小的尺寸與間距以節省面積,因而特別容易因ESD而失效,而由於電路內的VDD與VSS布線較長,容易造成一些離散的電阻(Rdd與RSS)與擴散電容(C),這些離散電阻和電容的分佈如圖1所示,造成該模式下的NDESD不易被旁路掉。

圖2所示為一ND模式的。ESD負電壓出現在輸出PAD上造成內部損傷的示意圖。當一ND模式的ESD負電壓出現在輸出PAD,在VDD接地輸出緩衝級內的PMOS元件會因電壓過高而擊穿導通來旁路ESD靜電電流。但在PMOS元件擊穿導通之前,該ND模式的ESD負電壓會先經由輸出緩衝級的NMOS元件傳遞到浮接的VSS電源線,因此原本出現在輸出與VDD之間的ESD負電壓會轉而降在VDD與VSS之間導致電路內部的ESD損傷。圖3為一正脈衝加於輸入而IC另一輸出相對接地,圖4為一負脈衝加於輸出對IC另一輸入相對接地的電流流向示意圖。圖3中可能造成輸入腳的ESD保護二極體Dnl崩潰來旁通ESD電流到浮接的VSS上,該電流再由輸出腳的NMOS寄生二極體Dn2流出。但是在:Dn2擊穿前,該ESD電流會先經由該輸入腳的另一ESD保護二極體Dp2而對浮接VDD充電,而浮接的VSS也會因輸出腳接地而被Dn2偏壓在接近地的電位,因此,發生在已輸入腳相對另一輸出腳的ESD電壓會轉變成在VDD與VSS之間的過電電壓,該電流會隨著VDD與VSS之間而進入集成電路內部而造成電路內部損傷,但輸入/輸出的ESD保護電路仍能完好無缺,ESD造成的內部損傷可能會使得VDD對VSS的漏電增加,也可能燒毀集成電路內部的元件而使得電路喪失部分的功能,這內部損傷要有功能測試才能找到損傷位置,而ESD造成的內部破壞的位置是一隨機現象,很難防範。圖4在負電壓下,浮接的VSS會因寄生在輸出NMOS的二極體Dn2而被偏壓到接近負ESD電壓,而浮接的VDD電源則被輸入到二極體Dpl偏壓在已接近地的電位。因此,原本出現住輸出對輸人的負電壓會變為VSS到VDD電源線之間的ESD電壓,而電壓會經VDD與VSS而進入集成電路內部,從而造成電路損傷。這種損傷方式比上面輸入/輸出對VDD和VSS情況更易發生,且不易有輸入到輸出的漏電發現,因此常在ESD測試儀上被誤判為正常元件。

為了箝制過高的ESD電壓跨在VDD與VSS電源線之間,須在二者之間設計保護電路。一大尺寸柵極接地的NMOS組件連接於IC的VDD與VSS電源線之間,被用來做VDD到VSS靜電放電防護電路。若有ESD電壓出現在VDD與VSS電源線之間,該NMOS組件將會崩潰導通來旁通該ESD的放電電流。但是,即使有該NMOS組件做.ESD防護組件來旁通ESD放電電流,IC的內部電路依然會出現ESD損傷的問題。因為,該NMOS組件除了提供ESD防護來保護IC內部電路之外,它也要能夠保護自己不被ESD電流所破壞,以免因其被ESD損毀而導致該IC無法正常使用。為了保護NMOS組件不被ESD電流所破壞,該NMOS組件通常在布局上便無法使用最小的布局間距。然而,IC的內部電路經常是使用最小的布局間距,這導致了一個問題,就是內部電路組件因具有最小的布局間距,會先崩潰導通,而ESD保護用電路中的NMOS元件因具有較大的布局間距,反而較慢崩潰導通,這使得柵極接地的NMOS組件不能夠有效地保護IC的內部電路。

(3)電源/地線上雜散電容/電阻效應

雖然深亞微米集成電路中的改良設計能夠充份保護IC內部電路,避免異常的ESD損傷。但是在電源/地線上的寄生電阻與電容效應會降低改良電路的保護效果。因為ESD放電現象在很短的時間內(約l00ns)便會出現高達數安培的放電電流,如果該改進ESD箝制電路的位置距離ESD的輸入或輸出腳位太遠,則可能會發生時間上來不及啟動保護電路的現象。在深亞微米VLSI中,晶元的尺寸越來越大,相對地環繞整個晶元的VDD與VSS電源線更長,其所相對產生的雜散電容/電阻效應也會增加,這反而降低了ESD箝制電路的防護效果。

(1)工藝上的改進

為了提高深亞微米集成電路的抗靜電能力,目前有ESD注入、金屬硅化物擴散層分隔和N阱電阻三種ESD保護改進工藝應用於深亞微米集成電路製造過程中。

為了克服因LDD結構所造成電路抗靜電能力的下降.便出現了ESD注入工藝。其原理是在同一電路上做出兩種不同的NMOS元件,一種是給內部電路單元使用,具有LDD結構的NMOS元件;另一種是給I/O使用,不具有LDD結構的NMOS元件。但利用ESD注入過程做的元件擁有較深的結面深度,故會有較嚴重的橫向擴散作用,所以利用ESD注入過程所作的NMOS元件不能用太短的溝道長度。此外利用ESD注入工藝做的NMOS元件與LDD結構的NMOS元件不同,故需要額外的處理及設計來提取這種ESD注入工藝NMOS元件的SPICE參數,以利於電路模擬與設計工作的進行。另外一種ESD注人工藝是將一摻雜濃度較高的硼注人到接觸孔正下方的N型擴區和P型襯底之間,以降低該結面的擊穿電壓。因為該結面具有較低的崩潰電壓,當靜電放電出現在NMOS元件的漏極時,靜電放電電流便會先由該低擊穿電壓的結面放電。利用這種工藝過程,NMOS元件仍可使用LDD結構且具有較短溝道長度,且該NMOS元件的SPICE參數跟其他NMOS元件相同,除了該結面擊穿電壓之外,不必另外抽取這種ESD注入的NMOS的SPICE參數。

為了提高輸出級的ESD能力,在工藝上還開發出了金屬硅化物擴散層分隔工藝。其原理是把輸出級用的NMOS元件中的金屬硅化物去除,使其源極和漏極的方塊電阻值回到30~40Ω/□,從而提高MOS元件的抗靜電能力。

在深亞微米集成電路製造工藝上還採用N阱電阻的方法來提高電路的抗靜電能力。原理是將輸出NMOS管漏極的N+擴區斷開,位於中間的N+擴區被連出當漏極,而斷開區域(場氧區域)利用N阱把中間的N+擴區連接到MOS管的漏極N+擴區上。此處N阱的作用用來限制ESD放電的瞬間峰值電流。另外在接觸孔下有N阱結構,可防止ESD電流造成漏極與P型襯底間短路。利用工藝上場氧區域的間距大小即可做出不同大小的N阱電阻,這種電阻會影響到輸出級的能力,但只要加大輸出級的元件寬度即可使其恢復到正常的推動能力。

(2)靜電保護元件上的改進

集成電路在生產工藝上的改進必將會增加電路製造的複雜程度和成本,如果能開發出不須改變工藝的靜電保護元件將具有更大的意義。低電壓觸發可控硅(Low Voltage Triggering SCR,簡稱LVTSCR)便是在單位面積下具有較高抗靜電能力的保護元件。利用這種元件,CMOS集成電路的抗靜電能力能夠只佔用很小面積便可達到較高的抗靜電能力。

SCR元件的基本結構如圖5所示。這種保護元件能在最小的布局面積下提供最高的ESD保護能力。但若只是簡單的四層結構,則此SCR元件起始導通電壓等於CMOS工藝下N阱和P襯底結面的擊穿電壓。由於N阱摻雜濃度較低,故其結面擊穿電壓在30~50V之間。具有如此高的結面擊穿電壓,使得SCR元件在ESD保護上需要加上第二級保護電路。第二級保護電路的目的在於提供較低電壓時的ESD保護能力。但第二級保護電路會佔用額外的布局面積,使得在PAD附近的版圖結構變得複雜。常用的第二級保護結構為一個短溝道的NMOS元件,結構如圖6所示。此改進SCR的起始導通電壓等於短溝道NMOS元件的擊穿電壓,大約在10~15V左右。其原理是利用內嵌的短溝道NMOS元件發生擊穿時,引發電流自N阱流向P襯底,因而觸發了SCR元件的導通。為了防止該保護元件在正常工作情況下不會被導通,其內含的短溝道NMOS的柵極連到地上,以保持該NMOS元件在電路正常工作時是關閉的。這種LVTSCR元件的ESD能力得以大幅度提高且不需要額外的工藝處理步驟,但其缺點是不易設計,需要相當的經驗才能夠充分使得原本是缺點的寄生元件變為ESD保護的元件。

在進行集成電路I/O埠對電源和地的靜電放電組合實驗中,在對地正脈衝(PS)、對地負脈衝(NS)、對電源正脈衝(PD)、對電源負脈衝(ND)四种放電模式中,PS和ND模式最易導致集成電路損傷。在以前的設計中,LVTSCR只被安排在PAD地的放電路徑上,故在先前的設計中仍欠缺對電源負脈衝保護的設計。

(3)電路改進方法

電路改進來提升集成電路的抗靜電能力,主要是利用ESD放電的瞬間電壓快速變化的特性,由電容耦合作用來使得ESD保護元件達到更好的保護作用。

1)柵極耦合技術

在深亞微米集成電路工藝中,元件的ESD能力下降,為了提升集成電路的抗靜電能力,在輸入/輸出PAD處的ESD保護元件或輸出級元件都會做得比較大,經常布圖為插指狀。但在ESD時,由於相對位置和布線方向不同並非所有插指能同時導通。所以即使元件尺寸已做得很大也未必能如預期地提升ESD保護能力。為了克服上述問題圖7、圖8給出了利用電容耦合作用來使大尺寸集成電路的每一插指都能均勻導通的設計。圖7為利用NMOS的擴散柵漏電容作耦合無件,另外一場氧元件加強了耦合電容的作用,當有正的ESD電壓時,瞬間電壓變化會導致NMOS柵極電壓跟著上升,由於電容耦合作用,因為NMOS柵極上有耦合的正電壓,故大尺寸NMOS元件的各個插指會一起進入擊穿區,因此其ESD防護能力便可充分發揮。

2)互補式柵極耦合技術

互補式柵極耦合技術是同時有對電源和地的柵極耦合NMOS元件。在任意I/O埠上的ESD放電有四種測試組合,所以ESD設計必須考慮這四種情況下的放電迴路。選擇合適的Cn(Cp)與Rn(Rp),能夠提供有效的ESD保護而不影響電路的正常工作狀態。圖9和圖10給出了此電路保護電路的原理圖和剖面結構圖,該耦合電容可以利用PAD與其下方的多晶層的寄生電容來實現,這樣設計可以節省電路布局面積。

3)深亞微米集成電路的VDD對VSS防護技術

為提升該NMOS組件的ESD保護功效,圖11為改良式的設計。在圖中,一靜電放電偵測電路被加入,用來控制該NMOS組件的柵極。當有ESD電壓出現跨在VDD與VSS電源線上時,該靜電放電偵測電路會送出一正電壓把NMOS組件導通來旁通掉ESD放電電流。由於該NMOS元件是藉由其柵極控制而導通,而不是像柵極接地NMOS組件是靠崩潰才導通的,因此具有極低的導通電壓。當內部電路組件尚未因ESD電壓崩潰之前,該NMOS組件就早已導通來旁通ESD放電電流了。這導通的NMOS組件在VDD與VSS之間成一暫時性的低阻抗狀態,因此跨在VDD與VSS之間的ESD電壓能夠很有效地被箝制住,不會再造成IC內部電路因ESD 而出現異常損壞的現象。利用此一改良式的ESD箝制電路,可以有效地防護腳對腳的ESD放電。當管腳對管腳ESD電壓轉變成跨在VDD與VSS電源線之間時,該RC控制的ESD偵測電路會因ESD的能量而偏壓工作,並送出正電壓到NMOS組件的柵極來導通該NMOS,ESD電流便經由這導通的NMOS組件而排放掉,因此IC的內部電路及寄生的SCR與BJT組件都不會因為ESD的過壓而破壞。

在深亞微米集成電路設計中,為了避免圖12所示這雜散電容/電阻的影響,電源線的寬度/長度與ESD 箝制電路的擺放位置需要建立一套設計準則,以利IC設計上的參考。

http://baike.eccn.com/eewiki/index.php/%E4%BA%9A%E5%BE%AE%E7%B1%B3%E5%92%8C%E6%B7%B1%E4%BA%9A%E5%BE%AE%E7%B1%B3MOS%E5%99%A8%E4%BB%B6