SOI

電路中元器件介質的隔離技術

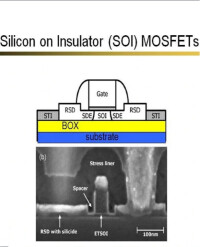

SOI全稱為Silicon-On-Insulator,即絕緣襯底上的硅,該技術是在頂層硅和背襯底之間引入了一層埋氧化層。

材料絕緣形半導薄膜,材料具硅擬優:集成電路中元器件的介質隔離,徹底消除了體硅CMOS電路中的寄生閂鎖效應;採用這種材料製成的集成電路還具有寄生電容小、集成密度高、速度快、工藝簡單、短溝道效應小及特別適用於低壓低功耗電路等優勢,因此可以說SOI將有可能成為深亞微米的低壓、低功耗集成電路的主流技術。此外,SOI材料還被用來製造MEMS光開關,如利用體微機械加工技術。

交換器的電子,有些會鑽入硅中造成浪費。SOI可防止電子流失。

全名為 Silicon On Insulator,是指硅晶體管結構在絕緣體之上的意思,原理就是在硅晶體管之間,加入絕緣體物質,可使兩者之間的寄生電容比原來的少上一倍。優點是可以較易提升時脈,並減少電流漏電成為省電的IC,在工藝上還可以省略部分光掩模以節省成本,因此不論在工藝上或是電路上都有其優勢。此外,在SOI晶圓(SOI wafer)本身襯底的阻抗值的部分也會影響到元件的表現,因此後來也有公司在襯底上進行阻抗值的調整,達到射頻元件(Radio frequency component、RF component)特性的提升。原本應通過交換器的電子,有些會鑽入硅中造成浪費;SOI可防止電子流失,與補強一些原本Bulk wafer中CMOS元件的缺點。摩托羅拉宣稱中央處理器可因此提升時脈20%,並減低耗電30%。除此之外,還可以減少一些有害的電氣效應。還有一點,可以說是很多超頻玩家所感興趣的,那就是它的工作溫度可高達300°C,減少過熱的問題。

SOI一開始是由美商IBM公司的晶元部門投入開發,最早用於Macintosh電腦(MAC)的PowerPC G4處理器,除了IBM外,還有Motorola、德州儀器(TI)、NEC等公司投入SOI技術的開發工作,但是Intel公司拒絕在其處理器產品中使用SOI技術,因為其認為SOI技術容易影響晶圓品質與減低晶體管交換速度,並且SOI上接合點也會減少,也就是一般工藝中“漏電”的缺點所煩惱。

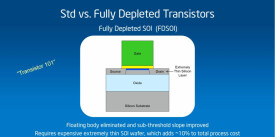

通常根據在絕緣體上的硅膜厚度將SOI分成薄膜全耗盡FD(Fully Depleted)結構和厚膜部分耗盡PD(Partially Depleted)結構。由於SOI的介質隔離,製作在厚膜SOI結構上的器件正、背界面的耗盡層之間不互相影響,在它們中間存在一中性體區,這一中性體區的存在使得硅體處於電學浮空狀態,產生了兩個明顯的寄生效應,一個是"翹曲效應"即Kink 效應,另一個是器件源漏之間形成的基極開路NPN寄生晶體管效應。如果將這一中性區經過一體接觸接地,則厚膜器件工作特性便和體硅器件特性幾乎完全相同。而基於薄膜SOI結構的器件由於硅膜的全部耗盡完全消除"翹曲效應",且這類器件具有低電場、高跨導、良好的短溝道特性和接近理想的亞閾值斜率等優點。因此薄膜全耗盡FDSOI應該是非常有前景的SOI結構。

Smart Cut process

除了特異的優點,在集成電路中使用外,還被用於微光機電MEMS系統的製造,如3D反射鏡陣列開關。該反射鏡是在SOI襯底的活性層中形成可動反射鏡,與另一台階狀電極的襯底連接而成。由於使用單晶硅襯底,且在可動反射鏡,直徑500微米,的上下面上對稱的以同一條件而形成反射膜等,因此,具有10納米級的翹曲與數十納米的表面粗糙度。

SOI 在器件性能上具有以下優點:

1) 減小了寄生電容,提高了運行速度。與體硅材料相比,SOI 器件的運行速度提高了20-35%;

2) 具有更低的功耗。由於減少了寄生電容,降低了漏電,SOI 器件功耗可減小35-70%;

3) 消除了閂鎖效應;

4) 抑制了襯底的脈衝電流干擾,減少了軟錯誤的發生;

5) 與現有硅工藝兼容,可減少 13-20%的工序。