共找到7條詞條名為FMC的結果 展開

- FPGA Mezzanine Card

- 美國以銷售製品為主的公司

- 飛行管理計算機簡稱

- 次世代網路

- 固定與移動融合

- FreePP免費視頻會議

- Future Mobility Corporation Ltd

FMC

FPGA Mezzanine Card

FMC:英文全稱,FPGA Mezzanine Card。是一個應用範圍、適應環境範圍和市場領域範圍都很廣的通用模塊。FMC連接器(FMC Connector)是FMC的一個重要組成部分,它連接由FPGA提供的引腳和FMC子板的I/O介面。最新的連接器技術維護的高性能引腳速度可以達到幾個Gb/s。

根據美國國家標準對FMC標準(American National Standard for FPGA Mezzanine Card (FMC) Standard, Approved July 2008)的規定內容,本詞條主要對商業級產品從以下三個方面對FMC作介紹:FMC 中間層模塊(FMC Mezzanine Module)、FMC載卡(FMC Carrier Card)和連接器引腳分配(Connector Pin Assignments)。

整個FMC模塊由子板模塊(或稱中間層模塊)、載卡兩部分構成。子板模塊和載卡之間由連接器連接;子板模塊上連接器使用公座(male),載卡上連接器使用母座(female)。載卡連接器引腳與具有可配置IO資源的晶元(例如,FPGA)引腳通過PCB設計連接在一起;子板模塊上連接器引腳與IO介面也是通過PCB設計連接起來。子板PCB上可以設計不同的IO介面實現不同的功能,這樣,同一個載卡可以通過子板的設計實現不同的擴展功能,使晶元的應用更加靈活。

此文檔提供的標準規定IO子板模塊可以但不限於用在3U和6U形狀因子卡上(form factor cards)。3U和6U形狀因子是VME機械標準中規定的標準尺寸。IO子板模塊連接的載卡支持:VME, VPX, VPX REDI, CompactPCI, CompactPCIExpress, Advanced TCA, AMC, PCI and PCI Express Carriers, PXI and PXI Express Carriers。

據此,FMC中每個模塊的機械尺寸規定如下:

• FMC Mezzanine Module:

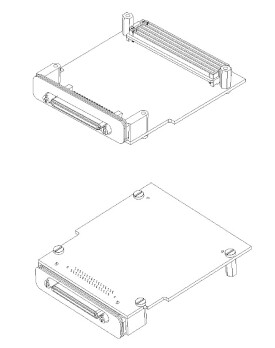

• IO 子板模塊有單寬(single width)和雙寬(double width)兩種尺寸,單寬的寬度為69mm,雙寬的寬度為139mm。單寬圖如概述中圖所示,雙寬圖如右圖所示。

![fmc[FPGA Mezzanine Card]](https://i1.twwiki.net/cover/w200/md/b/mdbf4e4938b85cc49df44cd9f589e3574.jpg)

fmc[FPGA Mezzanine Card]

子板模塊的PCB一般有三個區域:region1、region2、region3,如右圖所示。子板模塊的長度由組合的不同區域的長度疊加。

![fmc[FPGA Mezzanine Card]](https://i1.twwiki.net/cover/w200/m2/9/m294c28b8bacf9b1b2df40b80814132ac.jpg)

fmc[FPGA Mezzanine Card]

1、region1和2-典型應用於的氣冷商業級載卡上(air cooled commercial grade carrier cards)。

2、region2和3-典型應用於強化傳導冷卻載卡上(ruggedized conduction cooled carrier cards)。

3、region1、2和3-典型應用於需要區域1的強化導熱載卡。

之所以根據載卡類型來選擇子板模塊PCB區域,是由於在載卡上需要留齣子板模塊大小的區域用於放置子板模塊。

![fmc[FPGA Mezzanine Card]](https://i1.twwiki.net/cover/w200/mb/f/mbf3890f8048c21386d24d41ba27c2f27.jpg)

fmc[FPGA Mezzanine Card]

![fmc[FPGA Mezzanine Card]](https://i1.twwiki.net/cover/w200/me/6/me66833c83a9d0e9b5444d3309563229a.jpg)

fmc[FPGA Mezzanine Card]

![fmc[FPGA Mezzanine Card]](https://i1.twwiki.net/cover/w200/mb/b/mbbef00c9bf7ee5ba89b4e3687098e2c2.jpg)

fmc[FPGA Mezzanine Card]

載卡提供連接FMC子板模塊的插槽(slot),並且在載卡上預留恰當的空間給子板模塊,一般按照子板模塊的形狀來設計。

![fmc[FPGA Mezzanine Card]](https://i1.twwiki.net/cover/w200/m2/c/m2c006523b8920b58efe4c90d20e11fd5.jpg)

fmc[FPGA Mezzanine Card]

1、IO區域(如右圖陰影部分)、前面板支撐和連接器支架在載板上的區域不能放置任何元器件,有過孔也必須做絕緣處理;

2、子板模塊下方其餘區域在載卡上可以放置一些小型元器件,但最大高度有限制:對10mm高度的子板模塊不能超過4.7mm,8.5mm的不能超過3.2mm。

![fmc[FPGA Mezzanine Card]](https://i1.twwiki.net/cover/w200/m6/9/m6957ccd3b029421bf7849736f70b4ef6.jpg)

fmc[FPGA Mezzanine Card]

FMC的引腳分為電源信號引腳、JTAG信號引腳、IIC信號引腳、地址設置引腳、相應的控制檢測信號引腳、以及吉比特介面信號引腳(gigabit interface)和普通用戶信號引腳(user defined pins)及其時鐘信號引腳。其中的信號傳輸及其時鐘信號引腳都是按照差分對標準來定義的。

吉比特介面信號(用DP表示,data pairs)引腳有20對,能夠傳輸10組差分輸入輸出信號,其電平峰峰值不能超過1V,速度最大能夠設計到10Gbit/s。

普通用戶在使用時,FMC的部分引腳最好連接到同一個FPGA的Bank上面,保證其引腳電平相等。定義建議連到相同FPGA Bank的引腳分別稱為bank A、bank B。對於低引腳數的FMC其bank A信號有34對,高引腳數的有58對,分別可以傳輸17對和29對差分信號;而bank B只在高引腳數FMC上有,信號對引腳有22對,可以傳輸11對差分信號。用戶定義引腳信號電平採用LVDS和LVTTL信號標準,速度可以設計100Mbps到2Gbps。

FMC信號匹配阻抗按照單端50歐,差分100歐要求來設計。