邏輯門

集成電路上的基本組件

邏輯門(Logic Gates)是在集成電路(Integrated Circuit)上的基本組件。簡單的邏輯門可由晶體管組成。這些晶體管的組合可以使代表兩種信號的高低電平在通過它們之後產生高電平或者低電平的信號。高、低電平可以分別代表邏輯上的“真”與“假”或二進位當中的1和0,從而實現邏輯運算。

邏輯門

通過控制高、低電平(分別代表邏輯上的“真”與“假”或二進位當中的“1”和“0”),從而實現邏輯運算。

在最新研究中,英國帝國理工學院的科學家使用已經被修改過的DNA來對腸道內常見的大腸桿菌進行重新編程,讓其在受到化學物質的刺激時,能用蛋白質等作為輸入信息和輸出信息,完成邏輯運算,從而具有與當前計算機所用電路邏輯門類似的信息處理能力。他們研製出了一類“AND(與)門”,也製造出了一類“NOT(非)門”,並將兩者結合在一起製造出了更複雜的“與非門”。

最新研製出來的生物邏輯門的所作所為與電子邏輯門幾乎一樣,更重要的是,這種生物邏輯門可以模塊化地進行邏輯門之間的疊加,而以前的生物邏輯門則不具備這種邏輯門疊加功能,因此本次研究成果是科學家們迄今製造出的最先進的“生物電路”。

新型生物邏輯門的模塊化功能也意味著它們能被放在一起來製造不同類型的邏輯門,以便未來開發出更複雜的生物處理器。比如,科學家們可以研製出能在人的關節處遊盪的感測器,探測此處有害噬菌斑的組成並快速將藥物遞送到受影響的區域。其他應用還包括研製探測和破壞身體內癌細胞的感測器以及能置於環境中的污染檢測器來探測和中和諸如砷等有害毒素。

科學家們下一步計劃研製由多個邏輯門組成的更複雜的迴路。他們面臨的一個挑戰是找到方法能讓多個生物邏輯門有效地結合在一起,能像電子邏輯門之間那樣有效地“溝通”,以便執行更複雜的處理過程。

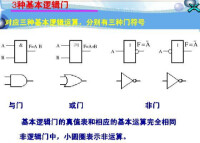

或門(英文:Or gate)又稱或電路。如果幾個條件中,只要有一個條件得到滿足,某事件就會發生,這種關係叫做“或”邏輯關係。具有“或”邏輯關係的電路叫做或門。或門有多個輸入端,一個輸出端,多輸入或門可由多個2輸入或門構成。只要輸入中有一個為高電平時(邏輯1),輸出就為高電平(邏輯1);只有當所有的輸入全為低電平時,輸出才為低電平。

與門(英語:AND gate)又稱“與電路”。是執行“與”運算的基本邏輯門電路。有多個輸入端,一個輸出端。當所有的輸入同時為高電平(邏輯1)時,輸出才為高電平,否則輸出為低電平(邏輯0)。

非門(英文:NOT gate)又稱反相器,是邏輯電路的基本單元,非門有一個輸入和一個輸出端。邏輯符號中輸出端的圓圈代表反相的意思。當其輸入端為高電平(邏輯1)時輸出端為低電平(邏輯0),當其輸入端為低電平時輸出端為高電平。也就是說,輸入端和輸出端的電平狀態總是反相的。

由與門與非門組合而成。

由或門和非門組合而成。

其中,非門和或非門在數字電路中較為常見。

設其中A和B為輸入變數

| 類型 | ANSI/IEEE標準 | IEC標準 | 又名/短釋 | 邏輯函數表示 | 真值表 | |

| NOT | 非門╱反相器: 逆轉輸入的高低狀態。 | A' | 輸入 A 1 | 輸出 An 1 | ||

| AND | 與門╱且門: 所有輸入為高時, 才會有輸出高。 | A*B | 輸入 A B 0 0 0 1 1 0 1 1 | 輸出 AandB 1 | ||

| NAND | 與非門: 與與門相反。 所有輸入為高時, 才會有輸出低。 | (A*B)' | 輸入 A B 0 0 0 1 1 0 1 1 | 輸出 AnandB 1 1 1 | ||

| OR | 或門: 所有輸入為低時, 才會有輸出低。 | A + B | 輸入 A B 0 0 0 1 1 0 1 1 | 輸出 AorB 1 1 1 | ||

| NOR | 或非門: 與或門相反。 所有輸入為低時, 才會有輸出高。 | (A + B)' | 輸入 A B 0 0 0 1 1 0 1 1 | 輸出 AnorB 1 | ||

| XOR | 異或門: 輸入相同時輸出為低, 否則為高。 | A'B + AB' | 輸入 A B 0 0 0 1 1 0 1 1 | 輸出 AxorB 1 1 | ||

| XNOR | 同或門: 與異或門相反。 輸入相同時輸出為高, 否則為低。 | AB + A'B' | 輸入 A B 0 0 0 1 1 0 1 1 | 輸出 AxnorB 1 1 | ||

把基本邏輯運算的電子電路稱之為邏輯門電路。在數字電路關係應用中,邏輯門電路中的門代表著基本邏輯關係的電路。

通過對邏輯門內部電路的源器件的差異,我們可以將其分為三大類,比較常用的就是CMOS 的邏輯門電路。

這種CMOS 邏輯門電路具備良好的應用效益,首先其功耗比較低,具備較低的應用成本,其電源電壓的範圍比較寬,邏輯度比較高,具備較強的抗干擾能力,其輸入阻抗比較高。MOS 門電路是由一系列的單極型MOS 管構成,其具備比較簡單的製造工藝,其功耗水平比較低,具備較高的集成度,其抗干擾能力強,比較適合進行大規模集成電路的應用。

在實踐過程中,MOS 門電路按照其MOS 管的應用不同,進行不同類型的劃分。CMOS 電路的應用優點比較特殊,其靜態功耗比較低,抗干擾能力強,工作具備較高的穩定性,其開關速度也是比較高的,因此其應用性比較廣泛。