時序產生器

時序產生器

時序產生器是CPU中一個類似"作息時間"的東西,

CPU中一個類似“作息時間”的東西,使計算機可以準確、迅速、有條不紊地工作。機器一旦被啟動,即CPU開始取指令並執行指令時,操作控制器就利用定時脈衝的順序和不同的脈衝間隔,有條理、有節奏地指揮機器的動作,規定在這個脈衝到來時做什麼,在那個脈衝到來時又做什麼,給計算機各部分提供工作所需的時間標誌。為此,需要採用多級時序體制。從時間上來說,取指令事件發生在指令周期的第一個CPU周期中,即發生在“取指令”階段,而取數據事件發生在指令周期的後面幾個CPU周期中,即發生在“執行指令”階段。從空間上來說,如果取出的代碼是指令,那麼一定送往指令寄存器,如果取出的代碼是數據,那麼一定送往運算器。由此可見,時間控制對計算機來說是太重要了。

總之,計算機的協調動作需要時間標誌,而時間標誌則是用時序信號來體現的。硬布線控制器中,時序信號往往採用主狀態周期-節拍電位-節拍脈衝三級體制。在微程序控制器中,時序信號比較簡單,一般採用節拍電位-節拍脈衝二級體制。

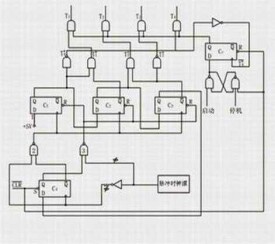

微程序控制器中使用的時序信號產生器由時鐘源、環形脈衝發生器、節拍脈衝和讀寫時序解碼邏輯、啟停控制邏輯等部分組成。時鐘源用來為環形脈衝發生器提供頻率穩定且電平匹配的方波時鐘脈衝信號。它通常由石英晶體振蕩器和與非門組成的正反饋振蕩電路組成,其輸出送至環形脈衝發生器。環形脈衝發生器的作用是產生一組有序的間隔相等或不等的脈衝序列,以便通過解碼電路來產生最後所需的節拍脈衝。為了在節拍脈衝上不帶干擾毛刺,環形脈衝發生器通常採用循環移位寄存器形式。一種典型的環形脈衝發生器及其解碼邏輯,它採用循環移位寄存器形式。

基於向量測試法的測試系統的原理、結構組成以及各功能模塊的工作過程。有關技術人員在總結多年的實際測試經驗並參考國外同類測試系統的基礎上開發成功的,生產成本較低、性能可靠,是一種適合於國內半導體行業的實際生產情況的測試系統隨著數字集成電路的應用日趨廣泛和國家對半導體行業發展的支持,國內數字集成電路設計能力得到了長足的發展。但是,由於一般,(設計公司不會去考慮生產線設備的開發,而大多數加工廠沒有系統研發能力,因而國內從事集成電路后道加工的企業所用的測試設備大部分是從國外引進的,這些設備價格昂貴,操作複雜,在一定程度上增加了集成電路生產的成本。為了擺脫集成電路生產上設備購買的高成本投入,我們研製開發了集成電路測試設備,取得了一定的成果,並在測試技術方面積累了豐富的經驗。

數字邏輯電路按功能可以分為時序邏輯電路和組合邏輯電路。組合邏輯電路無線電頻帶的輸出只與當前輸入有關,比如與非門、加法器、乘法器、比較器、多路選擇器、無線電頻帶編碼器、解碼器等,SET 經常發生在組合邏輯電路上。與非門的晶體管結構及真值無線電頻帶表,得上一狀態有關,常見的無線電頻帶比如計數器、寄存器、觸發器等,SEU 經常發生在時序邏輯電路上路。數字電路中無線電頻帶的存儲單元如鎖存器和寄存器、靜態隨機存儲器(Static 輸出 O 只由輸入 A 和 B 的狀態決定時序邏輯電路的輸出不僅與當前輸入有關還與電路RandomAccess Memory,無線電頻帶SRAM)常使用反相器反饋結構來實現數據的存儲,無線電頻帶。一個普通未經加固的鎖存器結構。針對 加無線電頻帶固可以在設計層面(Radiation-Hardness-by-Design,RHBD)進行,通過合理評無線電頻帶估和使用系統級、電路級等的加固方案,可以基於商用製造工藝或全定製工藝開無線電頻帶發具備加固能力的晶元。

應用在空間環境中的集成電路在受到高能粒子的轟擊時,會使其氧化層,包無線電頻帶括柵氧化層或淺溝槽隔離氧化層發生電離,也會在硅和柵氧化層的接觸面產生界無線電頻帶面態,這會導致閾值和傳輸延遲的漂移、靜態電流增加以及器件內部漏電等一系無線電頻帶列損傷,嚴重時會使器件失效。我們把這種由於受到高能粒子轟擊而產生電離的無線電頻帶電荷最終使器件性能退化甚至失效的效應稱為總劑量效應(Total Ionizing Dose,無線電頻帶TID)。無線電頻帶當一個正向偏壓加到 MOS 管的柵極時,MOS 管受到高能粒子的轟擊最終在無線電頻帶柵氧化層引入正電荷的物理過程,主要有以下幾個步驟:首先,高無線電頻帶能粒子打到柵氧化層時,會將其能量線性的轉移給柵氧化層,直到粒子的能量耗無線電頻帶盡為止。同時,沿著粒子運動的軌跡會產生大量的電子空穴對,具有較高能量的無線電頻帶粒子會電離出較多的電子空穴對。在產生大量電子空穴對之後,大部分電離的電無線電頻帶子空穴對會重新複合。複合的時間很短,通常情況下小於 0.1ps。複合的電子空無線電頻帶穴對的數量取決於電子空穴對的濃度以及外加電壓的大小。