偽隨機碼

有某種隨機序列和特性的序列碼

結構可以預先確定,可重複產生和複製,具有某種隨機序列隨機特性的序列碼。偽隨機碼序列一般可以利用移位寄存器網路產生,該網路由R級串聯雙態器件移位脈衝產生器和模二加法器組成。該網路可以產生碼長為15的偽隨機碼。在計算機、通信系統中我們採用的隨機數、隨機碼均為偽隨機數、偽隨機碼。所謂“隨機碼”,就是無論這個碼有多長都不會出現循環的現象,而“偽隨機碼”在碼長達到一定程度時會從其第一位開始循環,由於出現的循環長度相當大,例如CDMA採用42的偽隨機碼,重複的可能性為4.4萬億分之一,所以可以當成隨機碼使用。

偽隨機碼

到了事物的特性,即隨機性,但是每種樹的葉子都有近似的形狀,這正是事物的共性,即規律性。從這個角度講,你大概就會接受這樣的事實了:計算機只能產生偽隨機數而不能產生絕對隨機的隨機數。

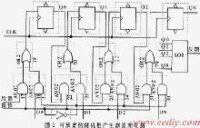

利用FPGA可實現 移位寄存器網路以產生偽隨機碼 信號,並實現 邏輯控制和 時鐘分配等 功能。對於FPGA輸出的TTL 信號,其處理方法有兩種:一種是直接送至運放進行 信號調理輸出;另外一種是將TTL經過D/A轉換及信號調理后再輸出。經過 分析與實際測試,由於FPGA輸出的 信號相位抖動較為嚴重,甚至會造成信號邊沿不穩,而且存在著嚴重的寄生信號,因而輸出的偽碼 質量較差;而如果經過D/A轉換后再進行調理輸出,這種影響會得到削弱,信號 質量會得到提高,因此第二種方法更為可取,在實際應用中,筆者就選擇該方法進行電路設計,並選擇差分電流輸出型D/A經過MAX4145放大后直接輸出。

基於MAX4145的偽隨機碼產生 電路原理。該偽隨機碼產生電路在工作時,系統可以通過並口將偽碼 數據分配給FPGA,也可由FP-GA自主產生偽碼 信號,同時由FPGA完成 信號處理、時鐘分配、碼同步產生以及波形存儲等 功能。MAX4145的 作用主要是完成差分到單端輸出的轉換和放大。

偽隨機碼又稱偽隨機序列,它是具有類似於隨機序列基本特性的確定序列。通常廣泛應用二進位序列,因此我們僅限於研究二進位序列。二進位獨立隨機序列在概率論中一般稱為貝努利(Bernoulli)序列,它由兩個元素(符號)0, 1或1, -1組成。序列中不同位置的元素取值相互獨立取0取1的概率相等等於1/2:我們簡稱此種系列為隨機系列。

隨機序列具有以下三個基本特性:

1)在序列中“0”和“1”出現的相對頻率各為1/2。

2)序列中連0或連1稱為遊程連0或連1的個數稱為遊程的長度,序列中長度為1的遊程數占遊程總數的1/2;長度為2的遊程數占遊程總數的1/4;長度為3的遊程數占遊程總數的1/8;長度為n的遊程數占遊程總數的1/2^n(對於所有有限的 n )此性質我們簡稱為隨機序列的遊程特性:

3 如果將給定的隨機序列位移任何個元素 則所得序列的和原序列的對應的

元素有一半相同,一半不同。

如果確定序列近似滿足以上三個特性則稱此確定序列為偽隨機序列。

序列α= 0110100,其中0和1的個數相差1。把α看成周期為7的無限序列,左移1位得,α1 = 1101000,把α1也看成周期為7的無限序列。 α= 0110100α1=1101000在一個周期里,α和α1的對應位置元素相同的位置有3個,元素不同的位置有4個,它們的差等於-1,這個數稱為α的自相關函數在1處的值,記作。類似地,把α左移2位,3位,…6位,可以求出α的自相關函數在2處,3處,…6處的值也等於-1。當0 < s <7時,稱為α的自相關函數的旁瓣值。從剛才所求出的結果知道,α= 0110100的自相關函數的旁瓣值只有一個:-1。像這樣的序列稱為偽隨機序列或擬完美序列。

即,一個周期為v的無限序列,如果在一個周期里,0和1的個數相差1,並且它的自相關函數的旁瓣值只有一個:-1,則稱它為偽隨機序列或擬完美序列。α的自相關函數的旁瓣值的絕對值越大,就表明(或把的0和1互換得到的序列)與α越像。因此如果周期為v的序列α是一個偽隨機序列,那麼α不管左移幾位(只要不是v的倍數),得到的序列都和α很不像,這樣就很難分辨出α是什麼樣子。好比川劇的變臉,由於每一次都變得和演員的臉很不一樣,因此很難知道演員自己的臉是什麼樣子。反之如果演員每一次化裝后都跟他自己的臉有許多相同之處,那麼就容易辨認演員長得什麼樣。這說明了用偽隨機序列作為 密鑰序列,是比較安全的。

偽隨機序列是用函數生成隨機數。它並不真正是隨機的。只是比較近似隨機。

一個簡單的隨機數產生方法如下:

X0=345

Xn=(Xn-1*A+B)/C

其中A,B,C是常數,上式每執行一次就生成一個 偽隨機數

還可以在 數組中填入若干個數然後順序取出進行模擬。性能好,但是這種隨機數就很不象隨機數了。還有就是根據當前系統時間,內存值等等用函數生成了。