IP核

特定電路功能的描述語言程序

IP核就是知識產權核或知識產權模塊的意思,在EDA技術開發中具有十分重要的地位。美國著名的Dataquest諮詢公司將半導體產業的IP定義為“用於ASIC或FPGA中的預先設計好的電路功能模塊”。IP主要分為軟IP、固IP和硬IP。軟IP是用Verilog/VHDL等硬體描述語言描述的功能塊,但是並不涉及用什麼具體電路元件實現這些功能。固IP是完成了綜合的功能塊。硬IP提供設計的最終階段產品——掩膜。

IP核

利用IP核設計電子系統,引用方便,修改基本元件的功能容易。具有複雜功能和商業價值的IP核一般具有知識產權,儘管IP核的市場活動還不規範,但是仍有許多集成電路設計公司從事IP核的設計、開發和營銷工作。

| Soft Cores(“code”)(軟核) | HDL語言描述 靈活度高,可修改 與工藝獨立,可根據具體的加工工藝重新綜合; IP很難保護 |

| Firm cores(“code+structure”)(固核) | 邏輯綜合后的描述 與工藝相關 布局和布線靈活 |

| Hard cores(“physical”)(硬核) | 物理綜合后的描述 準備流片 包含工藝相關的布局和時序信息 IP很容易保護 多數的處理器和存儲器 |

從20世紀90年代至今,IC設計能力正在發生一次質的飛躍,即由ASIC設計方法向SoC設計方法轉變。SoC設計方法使IC設計開始進一步分工細化,出現了IP設計和SoC系統設計。在近些年全球IC市場低迷的情況下,IP是不多的亮點之一。其實可以把IP理解為一顆ASIC,以前是ASIC做好以後供人家在PCB上使用,現在是IP做好以後讓人家集成在更大的晶元里。

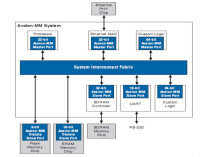

常用的IP內核模塊有各種不同的CPU(32/64位CISC/RISC結構的CPU或8/16位微控制器/單片機,如8051等)、32/64位DSP (如320C30)、DRAM、SRAM、EEPROM、Flashmemory、A/D、D/A、MPEG/JPEG、USB、PCI、標準介面、網路單元、編譯器、編碼/解碼器和模擬器件模塊等。豐富的IP內核模塊庫為快速地設計專用集成電路和單片系統以及儘快佔領市場提供了基本保證。

來源一:晶元設計公司的自身積累

IP核

來源二:Foundry的積累

Foundry廠商是沒有自身晶元產品的晶元代加工廠,但Foundry廠商為了吸引更多的晶元設計公司投片,往往設立後端設計隊伍,來配合後端設計能力較弱的晶元設計公司開展布局布線工作。這支設計隊伍也積累了一定的晶元設計經驗,並積累了少量的IP(主要是Memory、EEPROM和FlashMemory等),這些IP可以被需要集成或願意在該Foundry流片的公司採用。

此外,IP專職供應商與主要的Foundry廠商有長期的合作關係,經過投片驗證的IP可由Foundry廠向用戶提供,IP專職供應商從中提取一定利潤。但對國內用戶而言,因為這類Foundry多在我國台灣省,缺乏在本地的支持,可能有遠水不解近渴之憂。

來源三:專業IP公司

這是20世紀90年代中期興起的,迎接SoC時代到來的設計公司。這類公司的特點是已經認識到將自身多年積累的IP資源轉化成商品的商業價值,因此,它們不僅提供已經成熟的IP,同時針對當前的技術熱點、難點開發晶元設計市場急需的IP核。它們提供的IP同樣有硬核、固核、軟核之分,但通過與Foundry廠合作,及時對所開發的IP核進行流片驗證是IP硬核供應商的通行做法,這也是IP核及早面市的必要措施。

ARM、Motorola、MIPS是提供嵌入式MCUIP核的主要專業公司;LEDA是模擬、混合信號IP硬核的最主要供應商,它同時還針對當前通信市場的需求開發並提供寬頻應用、藍牙和光通信(SONET/SDH)的IP核。上述這些公司都是當今晶元設計行業中專業 IP供應商的代表。這些專業IP供應商的業務重點是開發IP核,對於進入自身所不熟悉的地區,則往往通過與當地的晶元設計服務公司結成合作夥伴或戰略聯盟來實現。

來源四:EDA廠商

在美國,EDA廠家也是提供IP資源的一個主要渠道,佔到IP交易量的10%左右。主要的EDA廠商為了提供更適合SoC設計的平台,在其工具中集成了各類 IP核以方便用戶的IP嵌入設計,這些IP核基本是以軟核形式出現。EDA廠商也並不直接設計開發IP核,而是與一些提供IP軟核的設計公司合作,提供一種集成IP核的設計環境。由於集成的IP核多為軟核,用戶還要對這些軟核做綜合、時序分析、驗證等工作,對用戶的"及時上市"要求沒有本質性改善,在IP核的支持、服務方面也存在諸多不便。因此,在國內的EDA廠家目前仍以經營EDA工具為主,從人員配備上講,幾乎沒有提供IP資源的服務力量。

來源五:設計服務公司

晶元設計服務公司是目前能立即向國內IC設計公司提供IP硬核的最主要途徑,除了自身積累的IP外,通過與IP專業供應商的戰略合作關係向國內用戶提供各類IP。

晶元設計服務公司是與用戶直接打交道的,它們了解市場需求的IP類型,其IP資源庫中積累的往往是最實用的IP。我國台灣省較有名的晶元設計服務公司有創意電子、智原科技等,它們除了積累了一定自己的IP硬核外,還與專業IP供應商,如ARM結成合作夥伴向用戶提供更豐富的IP資源。祖國大陸的晶元設計服務公司有泰鼎(上海),目前可為用戶提供300多種IP硬核,涉及高速數字邏輯、I/O模塊、模擬、混合信號、RF等領域。

目前,國內還沒有像國外那種專門設計IP硬核的公司,晶元設計公司的成功設計還不能被稱為IP。但國內已經有專門提供軟核的公司,以RTL的形式提供給用戶。

數字到模擬轉換器(DACS)將一個二進位數轉換為與之對應的電壓值,常用的D/A轉換器都是由電阻或電容加權網路、受碼元控制的開關和基準電壓或電流源組成。當D/A轉換器需要轉換的信號每次取樣字長很長時,對這些電路的精度要求很高,並且還必須在整個溫度範圍和整個使用壽命期間內保持電路參數的穩定。例如,一個16位的D/A轉換器,其MSB的精度必須在1/2 16以內,這是很困歲以內。所以,需尋求一種中保持高解析度又可降低對電路精度和穩定度要求的方法。

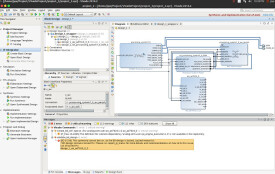

用VHDL語言編寫的程序

libraryieee;

useieeestd_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entitydac_ds is

port(reset :in std_logic;

clk:in std_logic;

din:in std_logic_vector(7 downto 0);--Signed integer

dout:out std_logic;

);

enddac_ds;

architecturearch_dac_ds of dac_ds is

signalerror :std_logic_vector(9 downto 0);--Error accumulator is 2 bits larger

constantzeros:std_logic_vector(7 downto 0):=(others=>'0');

begin

process(reset,clk,din)

variableval :std_logic_vector(9 downto 0);

begin

ifreset='1'then

error<=(others=>'0');

dout<='0';

elsifclk'event and clk='1' then

--val:=din+error;din is sign extended to nbits+2

val:=(din(din'high)&din(din'high)&din)+error;

ifval(val'high)='0'then

dout<='1';

error<=val+("11"& zeros);

else

dout<='0';

error<=val+("01"&zeros);

endif;

endif;

endprocess;

endarch_dac_ds;

選擇MAX7000S系列可編程邏輯器件,編譯後由MAX+PLUS II軟體自動配置進EMP7032SLC44晶元,將生成的目標文件通過編程電纜對器件進行編程。

將該IP核實現的D/A轉換器用於新型智能電阻爐溫度控制儀中,因為調節爐溫的信號不要求變化很快,因此DAC的輸入二進位信號為緩變信號。對於這種低頻應用,可以將RC時間常數取得較大,以減小雜訊。這樣,可綜合的VHDL語言Delta-Sigma DAC模塊配置進EMP7032晶元后,達到了預期的效果。

知識產權(IP)的再使用是設計組贏得迅速上市時間的主要策略,因為留給設計者完成諸如蜂窩電話和Internet路由器等熱門IC設計的周期只有3個月。設計者還需面對這樣一個嚴酷的現實,即IC的複雜度以每年55%的速率遞增,而設計能力每年僅提高21%。

為系統設計者專門製作的再使用IP彌補了這方面的不足。再使用既為IP建立者,也為系統設計者提供一種共享最佳IP核和主導模塊的方法。系統設計者的主要任務是在規定的周期時間內研發出複雜的設計。這隻有採用新設計方法和完全不同的晶元設計理念才能完成。IP再使用已經成為系統設計方法的關鍵所在。

標準是再使用的基礎。在設計一個系統時,可供工程人員考慮的工業標準很多,比如半導體再使用標準(SRS),它是對各種工業再使用創議標準的補充,提出這些創議標準的組織包括“虛插座介面聯盟VSIA”等。再使用標準為IP設計流程中的各階段提供規則、指南和介面方法。它是高效設計方法的一個里程碑,讓可再用IP快捷地、即插即用地集成到系統解決方案成為可能。

再使用標準通常涉及到許多方面,如系統級設計、結構、實現、驗證以及文件編製和可交付清單等與IP有關的事項。例如,結構分類目錄解決片上或片外的介面。實現分類目錄通過HDL代碼標準、物理表示、單元庫以及模擬子單元集中解決如何建立IP的問題。功能驗證及可測試設計(DFT)標準則包含在驗證分類目錄中。

根據IP使用的劃分,IP建立者可按下列三種形式設計IP:可再用、可重定目標以及可配置。可再用IP是著眼於按各種再使用標準定義的格式和快速集成的要求而建立的,便於移植,更重要的是有效集成。可重定目標IP是在充分高的抽象級上設計的,因而可以方便地在各種工藝與結構之間轉移。可配置IP是參數化后的可重定目標IP,其優點是可以對功能加以裁剪以符合特定的應用。這些參數包括匯流排寬度、存儲器容量、使能或禁止功能塊。硬IP與軟IP的意圖不同,因而對IP的開發和在這之後的IP的集成採用不同的方法。

硬IP對功率、體積和性能進行了優化,並映射至特定的工藝。具體實例包括已完成布局布線的網表,以特定工藝庫或全定製物理布圖,或兩者之組合。硬IP是特定工藝來實現的,通常用GDSII格式表示。硬IP可以再使用,且由於它已處於設計表示的最底層,因而最容易集成。硬IP已完全用目標工藝實現是按十分接近於標準單元庫元件的形式交付的,故而允許設計者將IP快速地集成在衍生產品中。硬IP最大的優點是確保性能,如速度、功耗等。然而難以轉移到新工藝或集成到新結構中,是不可重配置的。

軟IP是以綜合形式交付的,因而必須在目標工藝中實現,並由系統設計者驗證。其優點是源代碼的靈活性,它可重定目標於多種製作工藝,在新功能級中重新配置。

由於設計以高層次表示,因而軟IP是可再用的,易於重定目標和重配置,然而預測軟IP的時序、面積與功率諸方面的性能較困難。為了實現最高效率的再使用並減少集成時間,IP應從軟體源代碼開始;而為了確保性能,複雜IP應以硬IP的形式共享。

軟插接是開發符合再使用標準IP的過程,它應成為建立新IP設計流程的組成部分。過程需要有關IP深層的知識,因此只有IP建立者最熟知IP塊,有能力建立這些些概念,在時序分析時去除假通路,並最終確定結果的正確性。與DFT一樣,軟插接會修改現有的設計流程來適應再使用設計和生成附加可交付項,因此在設計流程中應及早考慮再使用事項。

IP資源庫為IP建立者和系統設計者提供共享和使用IP的基礎設施。這個系統應讓IP建立者和系統設計者共享硬和軟兩方面的可再用IP。資源庫提供多場所的全方位訪問,系統集成的全方位開發。它也是設計師搜索、選擇、將再使用塊集成到自己系統中的快捷而又簡便的途徑。

資源庫基礎設施還應開闢一個區域,讓系統開發者提供反饋、出錯報告、錯誤改正及資源庫中任何有關IP塊的註解。反饋信息塊建立者對錯誤的修復與改進說明一起是塊資料庫列表的一部分。

IP核

對IP核的再使用,建立者需軟插接IP、進行認證、將它存放在系統設計者能訪問的資源庫中。自動化工具提供多種手段,加速軟插接和資源庫的操作,認證和集成過程的部分自動化。工具製造商力爭實現更多的自動化。在理想情況下,全部IP塊可從資源庫中按需供給。

設計者幾乎沒有能力在一個月的設計設計周期內開發出合乎規格的新產品。如果對每個產品組建立一個設計平台,設計組就能充分發揮平台的作用,開發出產品的衍生品種。一種有效的再使用方法應讓可再使用IP的開發作為平台的一部分,並將IP塊快速地集成到衍生品種。

一旦IP開始普遍使用,提供該IP的支持是必要的。建立者繼續擁有IP,因為支持它需要深層的知識。建立者負責IP的更新,將最新版本放置在資源庫中。IP由為系統設計者服務的認證組重新認證。此外,建立者還應在系統設計者集成IP遇到困難時提供必需的支持。