儀錶放大器

源於運算放大器的差動放大器

儀錶放大器是一種精密差分電壓放大器,它源於運算放大器,且優於運算放大器。

隨著電子技術的飛速發展,運算放大電路也得到廣泛的應用。儀錶放大器把關鍵元件集成在放大器內部,其獨特的結構使它具有高共模抑制比、高輸入阻抗、低雜訊、低線性誤差、低失調漂移增益設置靈活和使用方便等特點,使其在數據採集、感測器信號放大、高速信號調節、醫療儀器和高檔音響設備等方面倍受青睞。儀錶放大器是一種具有差分輸入和相對參考端單端輸出的閉環增益組件,具有差分輸出和相對參考端的單端輸出。與運算放大器不同之處是運算放大器的閉環增益是由反相輸入端與輸出端之間連接的外部電阻決定,而儀錶放大器則使用與輸入端隔離的內部反饋電阻網路。儀錶放大器的 2 個差分輸入端施加輸入信號,其增益即可由內部預置,也可由用戶通過引腳內部設置或者通過與輸入信號隔離的外部增益電阻預置。

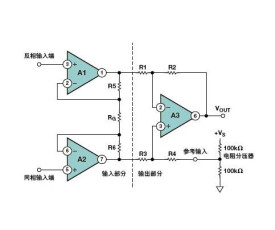

儀錶放大器電路的典型結構如圖1所示。它主要由兩級差分放大器電路構成。其中,運放A1,A2為同相差分輸入方式,同相輸入可以大幅度提高電路的輸入阻抗,減小電路對微弱輸入信號的衰減;差分輸入可以使電路只對差模信號放大,而對共模輸入信號只起跟隨作用,使得送到后級的差模信號與共模信號的幅值之比(即共模抑制比CMRR)得到提高。這樣在以運放A3為核心部件組成的差分放大電路中,在CMRR要求不變情況下,可明顯降低對電阻R3和R4,Rf和R5的精度匹配要求,從而使儀錶放大器電路比簡單的差分放大電路具有更好的共模抑制能力。在R1=R2,R3=R4,Rf=R5的條件下,圖1電路的增益為:G=(1+2R1/Rg)(Rf/R3)。由公式可見,電路增益的調節可以通過改變Rg阻值實現。

儀錶放大器

目前,儀錶放大器電路的實現方法主要分為兩大類:第一類由分立元件組合而成;另一類由單片集成晶元直接實現。根據現有元器件,分別以單運放LM741和OP07,集成四運放LM324和單片集成晶元AD620為核心,設計出四種儀錶放大器電路方案。

儀錶放大器

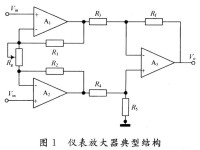

圖2中的A1~A3分別用LM741替換即可。電路的工作原理與典型儀錶放大器電路完全相同。

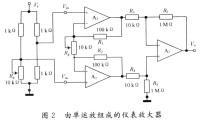

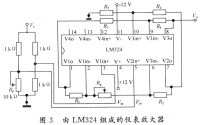

方案2 由3個精密運放OP07組成,電路結構與原理和圖2相同(用3個OP07分別代替圖2中的A1~A3)。 方案3 以一個四運放集成電路LM324為核心實現,如圖3所示。它的特點是將4個功能獨立的運放集成在同一個集成晶元里,這樣可以大大減少各運放由於製造工藝不同帶來的器件性能差異;採用統一的電源,有利於電源雜訊的降低和電路性能指標的提高,且電路的基本工作原理不變。

方案3 以一個四運放集成電路LM324為核心實現,如圖3所示。它的特點是將4個功能獨立的運放集成在同一個集成晶元里,這樣可以大大減少各運放由於製造工藝不同帶來的器件性能差異;採用統一的電源,有利於電源雜訊的降低和電路性能指標的提高,且電路的基本工作原理不變。

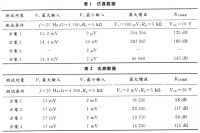

儀錶放大器

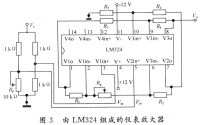

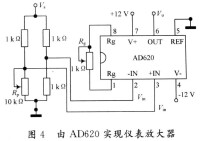

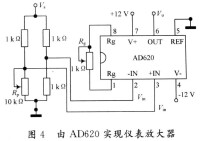

方案4 由一個單片集成晶元AD620實現,如圖4所示。它的特點是電路結構簡單:一個AD620,一個增益設置電阻Rg,外加工作電源就可以使電路工作,因此設計效率最高。圖4中電路增益計算公式為:G=49.4K/Rg+1。 實現儀錶放大器電路的四種方案中,都採用4個電阻組成電橋電路的形式,將雙端差分輸入變為單端的信號源輸入。性能測試主要是從信號源Vs的最大輸入和Vs最小輸入、電路的最大增益及共模抑制比幾方面進行模擬和實際電路性能測試。測試數據分別見表1和表2。其中,Vs最大(小)輸入是指在給定測試條件下,使電路輸出不失真時的信號源最大(小)輸入;最大增益是指在給定測試條件下,使輸出不失真時可以實現的電路最大增益值。共模抑制比由公式KCMRR=20|g | AVD/AVC|(dB)計算得出。

實現儀錶放大器電路的四種方案中,都採用4個電阻組成電橋電路的形式,將雙端差分輸入變為單端的信號源輸入。性能測試主要是從信號源Vs的最大輸入和Vs最小輸入、電路的最大增益及共模抑制比幾方面進行模擬和實際電路性能測試。測試數據分別見表1和表2。其中,Vs最大(小)輸入是指在給定測試條件下,使電路輸出不失真時的信號源最大(小)輸入;最大增益是指在給定測試條件下,使輸出不失真時可以實現的電路最大增益值。共模抑制比由公式KCMRR=20|g | AVD/AVC|(dB)計算得出。

儀錶放大器

儀錶放大器

(2)表格中的電壓測量數據全部以峰峰值表示;

(3)由於模擬器件原因,實驗中用Multisim對方案3的模擬失效,表1中用“-”表示失效數據;

(4)表格中的方案1~4依次分別表示以LM741,OP07,LM324和AD620為核心組成的儀錶放大器電路。

由表1和表2可見,模擬性能明顯優於實際測試性能。這是因為模擬電路的性能基本上是由模擬器件的性能和電路的結構形式確定的,沒有外界干擾因素,為理想條件下的測試;而實際測試電路由於受環境干擾因素(如環境溫度、空間電磁干擾等)、人為操作因素、實際測試儀器精確度、準確度和量程範圍等的限制,使測試條件不夠理想,測量結果具有一定的誤差。在實際電路設計過程中,模擬與實際測試各有所長。一般先通過模擬測試,初步確定電路的結構及器件參數,再通過實際電路測試,改進其具體性能指標及參數設置。這樣,在保證電路功能、性能的前提下,大大提高電路設計的效率。

由表2的實測數據可以看出:方案2在信號輸入範圍(即Vs的最大、最小輸入)、電路增益、共模抑制比等方面的性能表現為最優。在價格方面,它比方案1和方案3的成本高一點,但比方案4便宜很多。因此,在四種方案中,方案2的性價比最高。方案4除最大增益相對小點,其他性能僅次於方案2,具有電路簡單,性能優越,節省設計空間等優點。成本高是方案4的最大缺點。方案1和方案3在性能上的差異不大,方案3略優於方案1,且它們同時具有絕對的價格優勢,但性能上不如方案2和方案4好。

綜合以上分析,方案2和方案4適用於對儀錶放大器電路有較高性能要求的場合,方案2性價比最高,方案4簡單、高效,但成本高。方案1和方案3適用於性能要求不高且需要節約成本的場合。針對具體的電路設計要求,選取不同的方案,以達到最優的資源利用。電路的設計方案確定以後,在具體的電路設計過程中,要注意以下幾個方面:

(1)注意關鍵元器件的選取,比如對圖2所示電路,要注意使運放A1,A2的特性儘可能一致;選用電阻時,應該使用低溫度係數的電阻,以獲得儘可能低的漂移;對R3,R4,R5和R6的選擇應儘可能匹配。

(2)要注意在電路中增加各種抗干擾措施,比如在電源的引入端增加電源退耦電容,在信號輸入端增加RC低通濾波或在運放A1,A2的反饋迴路增加高頻消噪電容,在PCB設計中精心布局合理布線,正確處理地線等,以提高電路的抗干擾能力,最大限度地發揮電路的性能。

● 高共模抑制比

共模抑制比(CMRR) 則是差模增益( A d) 與共模增益( Ac) 之比,即:CMRR = 20lg | Ad/ Ac | dB ;儀錶放大器具有很高的共模抑制比,CMRR 典型值為 70~100 dB 以上。

● 高輸入阻抗

要求儀錶放大器必須具有極高的輸入阻抗,儀錶放大器的同相和反相輸入端的阻抗都很高而且相互十分平衡,其典型值為 109~1012Ω.

● 低雜訊

由於儀錶放大器必須能夠處理非常低的輸入電壓,因此儀錶放大器不能把自身的雜訊加到信號上,在 1 kHz 條件下,摺合到輸入端的輸入雜訊要求小於 10 nV/ Hz.

● 低線性誤差

輸入失調和比例係數誤差能通過外部的調整來修正,但是線性誤差是器件固有缺陷,它不能由外部調整來消除。一個高質量的儀錶放大器典型的線性誤差為 0. 01 % ,有的甚至低於 0. 0001 %.

● 低失調電壓和失調電壓漂移

儀錶放大器的失調漂移也由輸入和輸出兩部分組成,輸入和輸出失調電壓典型值分別為 100μV 和2 mV.

雙極型輸入運算放大器的基極電流,FET 型輸入運算放大器的柵極電流,這個偏置電流流過不平衡的信號源電阻將產生一個失調誤差。雙極型輸入儀錶放大器的偏置電流典型值為 1 nA~50 pA ;而 FET 輸入的儀錶放大器在常溫下的偏置電流典型值為 50 pA.

● 充裕的帶寬

儀錶放大器為特定的應用提供了足夠的帶寬,典型的單位增益小信號帶寬在 500 kHz~4 MHz 之間。

● 具有“檢測”端和“參考”端

儀錶放大器的獨特之處還在於帶有“檢測”端和“參考”端,允許遠距離檢測輸出電壓而內部電阻壓降和地線壓降( IR) 的影響可減至最小。